Dual Channel Photologic Encoder Detector

... Two matched detectors with photolithographic control of relative position Dual Photologic® circuitry in single package provides reduced component count Open collector inverter output for flexibility of circuit interface Low cost plastic housing ...

... Two matched detectors with photolithographic control of relative position Dual Photologic® circuitry in single package provides reduced component count Open collector inverter output for flexibility of circuit interface Low cost plastic housing ...

E-308 - Accuphase

... such as convenient operation and modest space requirements. However, because its overall gain is very high, even the slightest interference or crosstalk at the input can have a considerable effect on the sonic result. To preclude this possibility, the E-308 is designed to achieve total electrical an ...

... such as convenient operation and modest space requirements. However, because its overall gain is very high, even the slightest interference or crosstalk at the input can have a considerable effect on the sonic result. To preclude this possibility, the E-308 is designed to achieve total electrical an ...

PART B UNIT I (i). State and prove Demorgan`s law (6) (EI May 2007

... 13.(i) Implement the following Boolean function using suitable multiplexer F(A,B,C)= Ʃm(1,3,5,6) (8) (ii) Design full subtractor using half subtractor(8) (EI May/june 2013) 14. (i) Design a code converters for BCD to gray code converters (10) (ii)Explain how the demultiplexer used as decoder.(6) (E ...

... 13.(i) Implement the following Boolean function using suitable multiplexer F(A,B,C)= Ʃm(1,3,5,6) (8) (ii) Design full subtractor using half subtractor(8) (EI May/june 2013) 14. (i) Design a code converters for BCD to gray code converters (10) (ii)Explain how the demultiplexer used as decoder.(6) (E ...

UA741CP

... For R1 = 100, 1k, 10k, and 100k Ohms, both compute and measure the gain for this amplifier by comparing Vout / Vinput to 10k Ohms/R1. You may need to vary the input voltage to see the gain correctly (probably need it to be smaller). For R1 = 1k, look at In+ and In− with an oscilloscope probe. You sh ...

... For R1 = 100, 1k, 10k, and 100k Ohms, both compute and measure the gain for this amplifier by comparing Vout / Vinput to 10k Ohms/R1. You may need to vary the input voltage to see the gain correctly (probably need it to be smaller). For R1 = 1k, look at In+ and In− with an oscilloscope probe. You sh ...

EMAC single board controller interfaceing guidelines.

... have seen this when switching a light switch, you will see and hear it arching for a short period of time until it settles. For example if we have a switch with a pull-up resistor connected as described above, when the switch is flipped to the on position it will initially bounce between high and lo ...

... have seen this when switching a light switch, you will see and hear it arching for a short period of time until it settles. For example if we have a switch with a pull-up resistor connected as described above, when the switch is flipped to the on position it will initially bounce between high and lo ...

wogglebugmanual.

... The Wogglebug is a random voltage generator, originally designed by Grant Richter of Wiard Synthesizers. The Wogglebug's purpose is to overtake the control voltages produced by your keyboard or sequencer during performance and give a voice to your synthesizer's ID. It is your synthesizer's ID MONSTE ...

... The Wogglebug is a random voltage generator, originally designed by Grant Richter of Wiard Synthesizers. The Wogglebug's purpose is to overtake the control voltages produced by your keyboard or sequencer during performance and give a voice to your synthesizer's ID. It is your synthesizer's ID MONSTE ...

Zero Transfer Time Ferroresonant UPS

... Power Supplies (UPS) for Cable TV and Broadband communication networks in two-way digital transmission. The PZM9500 Series’ advanced C.V.T. Ferroresonant technology provides the high efficiency regulated AC quasi-square wave with field-selectable output voltage, stable frequency, surge & short circu ...

... Power Supplies (UPS) for Cable TV and Broadband communication networks in two-way digital transmission. The PZM9500 Series’ advanced C.V.T. Ferroresonant technology provides the high efficiency regulated AC quasi-square wave with field-selectable output voltage, stable frequency, surge & short circu ...

Programmable Low Voltage 1:10 LVDS Clock Driver ADN4670

... Programming is enabled by taking EN high. The data on SI is then clocked into the device on each 0-to-1 transition of CK. Data on SI must be stable for the setup time (tSU) before the clock transition and remain stable for the hold time (tH) after the clock transition. To program the device, 11 bits ...

... Programming is enabled by taking EN high. The data on SI is then clocked into the device on each 0-to-1 transition of CK. Data on SI must be stable for the setup time (tSU) before the clock transition and remain stable for the hold time (tH) after the clock transition. To program the device, 11 bits ...

800-5615.......... TC-3 Tortoise Turnout Control

... The TC-3 has two control terminals and may be used to independently control both directions of a turnout. In this way, the output from one detection circuit may be used to throw the TORTOISE one way, and the output of another detection circuit used to throw it back. The TC-3 is also ideal as an inte ...

... The TC-3 has two control terminals and may be used to independently control both directions of a turnout. In this way, the output from one detection circuit may be used to throw the TORTOISE one way, and the output of another detection circuit used to throw it back. The TC-3 is also ideal as an inte ...

Data Sheet

... signal are being used to clock the data; if only one edge were used, the clock signal would need to be twice as fast. Propagation delay skew represents the uncertainty of where an edge might be after being sent through an optocoupler. Figure 15 shows that there will be uncertainty in both the data a ...

... signal are being used to clock the data; if only one edge were used, the clock signal would need to be twice as fast. Propagation delay skew represents the uncertainty of where an edge might be after being sent through an optocoupler. Figure 15 shows that there will be uncertainty in both the data a ...

Considerations and designs for a system of tdc`s with

... Considerations and designs for a system of tdc’s with 1psec resolution ...

... Considerations and designs for a system of tdc’s with 1psec resolution ...

MC100ES8111, Low Voltage 1:10 Differential HSTL Clock Fanout

... outputs are used, the output pairs on the same package side as the parts being used on that side should be terminated. The HSTL compatible output levels are generated with an open emitter architecture. This minimizes part-to-part and output-to-output skew. The open-emitter outputs require a 50 Ω DC ...

... outputs are used, the output pairs on the same package side as the parts being used on that side should be terminated. The HSTL compatible output levels are generated with an open emitter architecture. This minimizes part-to-part and output-to-output skew. The open-emitter outputs require a 50 Ω DC ...

DM7407 Hex Buffers with High Voltage Open

... Hex Buffers with High Voltage Open-Collector Outputs General Description This device contains six independent gates each of which performs a buffer function. The open-collector outputs require external pull-up resistors for proper logical operation. ...

... Hex Buffers with High Voltage Open-Collector Outputs General Description This device contains six independent gates each of which performs a buffer function. The open-collector outputs require external pull-up resistors for proper logical operation. ...

DGD

... • Power must be applied externally to the anode connection that is common to all the segments • By applying the ground to a particular segment (i.e. a,b,g etc..), the appropriate segment will light up ...

... • Power must be applied externally to the anode connection that is common to all the segments • By applying the ground to a particular segment (i.e. a,b,g etc..), the appropriate segment will light up ...

§7 Designing with Logic

... One critical application area is bus contention during the power-on phase of a system. This bus contention occurs because, during the power-on phase (system reset), the supervising circuit does not provide defined control signals even though the rest of the system may already be functional. Therefor ...

... One critical application area is bus contention during the power-on phase of a system. This bus contention occurs because, during the power-on phase (system reset), the supervising circuit does not provide defined control signals even though the rest of the system may already be functional. Therefor ...

design of low power test pattern generator

... density and performance. The XOR gate forms the basic building blocks of various digital VLSI circuits like full adder, multiplier, comparator and parity checker. Enhancing the performance of the XOR gates can significantly improve the performance of the system as whole. The design of this gate has ...

... density and performance. The XOR gate forms the basic building blocks of various digital VLSI circuits like full adder, multiplier, comparator and parity checker. Enhancing the performance of the XOR gates can significantly improve the performance of the system as whole. The design of this gate has ...

Data Sheet - Asahi Kasei Microdevices

... indicated under “Recommended Operating Conditions” is not implied. Exposure to absolute-maximum-rating conditions for extended periods may affect device reliability. Electrical parameters are guaranteed only over the ...

... indicated under “Recommended Operating Conditions” is not implied. Exposure to absolute-maximum-rating conditions for extended periods may affect device reliability. Electrical parameters are guaranteed only over the ...

HMC723LC3C 数据资料DataSheet下载

... operation, data is transferred to the outputs on the positive edge of the clock. Reversing the clock inputs allows for negative-edge triggered applications. The HMC723LC3C also features an output level control pin, VR, which allows for loss compensation or for signal level optimization. All input si ...

... operation, data is transferred to the outputs on the positive edge of the clock. Reversing the clock inputs allows for negative-edge triggered applications. The HMC723LC3C also features an output level control pin, VR, which allows for loss compensation or for signal level optimization. All input si ...

STLVD111B

... Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries (“ST”) reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notic ...

... Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries (“ST”) reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notic ...

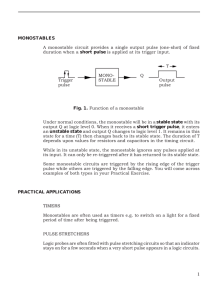

1 MONOSTABLES A monostable circuit provides a single output

... Under normal conditions, the monostable will be in a stable state with its output Q at logic level 0. When it receives a short trigger pulse, it enters an unstable state and output Q changes to logic level 1. It remains in this state for a time (T) then changes back to its stable state. The duration ...

... Under normal conditions, the monostable will be in a stable state with its output Q at logic level 0. When it receives a short trigger pulse, it enters an unstable state and output Q changes to logic level 1. It remains in this state for a time (T) then changes back to its stable state. The duration ...

iC-OV BLCC OVC3 - iC-Haus

... Card shows >20% when read at 23°C ±5°C or if the conditions mentioned above are not met. Devices may be baked for 72 hours at 100°C using high-temperature device containers (trays). Samples Samples are not substitute for dry pack delivery and are not intended for reflow soldering. Remove any protect ...

... Card shows >20% when read at 23°C ±5°C or if the conditions mentioned above are not met. Devices may be baked for 72 hours at 100°C using high-temperature device containers (trays). Samples Samples are not substitute for dry pack delivery and are not intended for reflow soldering. Remove any protect ...

MM74C925 * MM74C926 4-Digit Counters with Multiplexed 7

... Segment resistors are desirable to minimize power dissipation and chip heating. The DS75492 serves as a good digit driver when it is desired to drive bright displays. When using this driver with a 5V supply at room temperature, the display can be driven without segment resistors to full illumination ...

... Segment resistors are desirable to minimize power dissipation and chip heating. The DS75492 serves as a good digit driver when it is desired to drive bright displays. When using this driver with a 5V supply at room temperature, the display can be driven without segment resistors to full illumination ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.