exam1f03wSolutions

... An address (base) is accessed from a register and is added to an immediate part (offset) to give the address where the desired data item is stored. This is used in MIPS in load and store instructions as with ls $r1, val($r2) where $r2 is the register with the base address that is added to the immedi ...

... An address (base) is accessed from a register and is added to an immediate part (offset) to give the address where the desired data item is stored. This is used in MIPS in load and store instructions as with ls $r1, val($r2) where $r2 is the register with the base address that is added to the immedi ...

C7-2 56Gb/s PAM4 and NRZ SerDes Transceivers in 40nm CMOS

... 4. Here, we present a full-rate purely-linear NRZ CDR/DEMUX operating at 56Gb/s. After pre-amplification and equalization, the input data goes through a static divided-by-2 circuit to slow down the high-speed data by a factor of 2. The data transitions are still preserved but split into two interlea ...

... 4. Here, we present a full-rate purely-linear NRZ CDR/DEMUX operating at 56Gb/s. After pre-amplification and equalization, the input data goes through a static divided-by-2 circuit to slow down the high-speed data by a factor of 2. The data transitions are still preserved but split into two interlea ...

DN400 - True Rail-to-Rail, High Input Impedance ADC Simplifies

... with a charge reservoir to average the ADC’s sampling current while the 2.5k feedback resistor maintains DC accuracy. The LTC6241 has a rail-to-rail output stage, and an input common mode range from the negative supply to 1.5V lower than the positive supply. Since no rail-to-rail amplifier can actual ...

... with a charge reservoir to average the ADC’s sampling current while the 2.5k feedback resistor maintains DC accuracy. The LTC6241 has a rail-to-rail output stage, and an input common mode range from the negative supply to 1.5V lower than the positive supply. Since no rail-to-rail amplifier can actual ...

A 24 Vin, 40 Watt, Low Cost, DC-to-DC Converter

... amp output version. Other output voltages from 3.3 up to 28 Vdc are easy to implement by modifying the values (or ratings) of R8, R11, R12, C9, D5 and T1’s secondary turns. ...

... amp output version. Other output voltages from 3.3 up to 28 Vdc are easy to implement by modifying the values (or ratings) of R8, R11, R12, C9, D5 and T1’s secondary turns. ...

Physics 517/617 Experiment 6A Digital Circuits

... to signal a high or low state. What is the output voltage of a high or low state? 2) Verify the truth table for the JK flipflop (74S112) including reset and clear options. 3) Using 3 J-K flipflops build a circuit that counts from zero to seven, i.e. 0, 1, 2, 3, 4, 5, 6, 7, 0, … Using the oscilloscop ...

... to signal a high or low state. What is the output voltage of a high or low state? 2) Verify the truth table for the JK flipflop (74S112) including reset and clear options. 3) Using 3 J-K flipflops build a circuit that counts from zero to seven, i.e. 0, 1, 2, 3, 4, 5, 6, 7, 0, … Using the oscilloscop ...

MHY 923 - Input/output device

... It contains one separately controllable bi-stable relay and one input for transmission of information to the C.I.E. This input allows checking of connected outer device controlled by built-in relay, or it is possible to set output as independent. On this output it is possible to connect e.g. aspirat ...

... It contains one separately controllable bi-stable relay and one input for transmission of information to the C.I.E. This input allows checking of connected outer device controlled by built-in relay, or it is possible to set output as independent. On this output it is possible to connect e.g. aspirat ...

NTE4018B Integrated Circuit CMOS, Presettable Divide−By−N

... 16−Lead DIP Type Package Description: The NTE4002B contains five Johnson counter stages which are asynchronously presettable and resettable. The counters are synchronous, and increment on the positive going edge of the clock. Presetting is accomplished by a logic “1” on the preset enable input. Data ...

... 16−Lead DIP Type Package Description: The NTE4002B contains five Johnson counter stages which are asynchronously presettable and resettable. The counters are synchronous, and increment on the positive going edge of the clock. Presetting is accomplished by a logic “1” on the preset enable input. Data ...

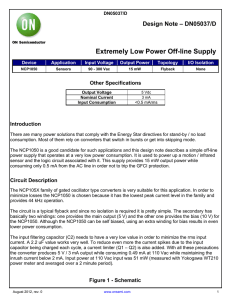

Extremely Low Power Off-line Supply

... There are many power solutions that comply with the Energy Star directives for stand-by / no load consumption. Most of them rely on converters that switch in bursts or get into skipping mode. The NCP1050 is a good candidate for such applications and this design note describes a simple off-line power ...

... There are many power solutions that comply with the Energy Star directives for stand-by / no load consumption. Most of them rely on converters that switch in bursts or get into skipping mode. The NCP1050 is a good candidate for such applications and this design note describes a simple off-line power ...

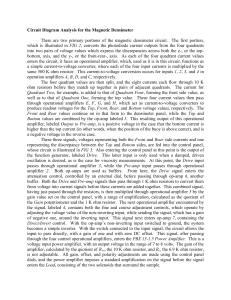

THAT Corporation Design Note 108

... This setting will result in the RMS detector having zero volts out when the input signal level is -10dBu ( corresponding to unity gain in the VCA). The threshold amplifier has been modified to have an offset injected through R5 that sets the nominal threshold to -40 dBu, and VR2 allows this level to ...

... This setting will result in the RMS detector having zero volts out when the input signal level is -10dBu ( corresponding to unity gain in the VCA). The threshold amplifier has been modified to have an offset injected through R5 that sets the nominal threshold to -40 dBu, and VR2 allows this level to ...

Example 16 - Rose

... In this problem, we want to design a circuit having three inputs v1 , v 2 , and v 3 , and one output v out .The output must be related to the inputs by vout 3v1 5v 2 4v3 . This required circuit must multiply each input by a number and add the results. The polarity of the first two input volta ...

... In this problem, we want to design a circuit having three inputs v1 , v 2 , and v 3 , and one output v out .The output must be related to the inputs by vout 3v1 5v 2 4v3 . This required circuit must multiply each input by a number and add the results. The polarity of the first two input volta ...

raise - lower (set-point) / ramp generator

... no further action. Active states of input signals are indiviually programmble. Output options Four ramp types are available each of which may be set to generate a single period waveform or, using the repeat option, a continuous waveform. Other options enable the ramp to start when power is applied a ...

... no further action. Active states of input signals are indiviually programmble. Output options Four ramp types are available each of which may be set to generate a single period waveform or, using the repeat option, a continuous waveform. Other options enable the ramp to start when power is applied a ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.