energy recovery flip-flops and resonant clocking of sccer flip

... occurs. In this phase the difference between (DATA (D) and DATAB (DB) result in small voltage difference between set and reset nodes which is amplified by cross coupled inverter and as a result either set or reset node switches to low. When M3 and M5 are on, SET node will be discharge through three ...

... occurs. In this phase the difference between (DATA (D) and DATAB (DB) result in small voltage difference between set and reset nodes which is amplified by cross coupled inverter and as a result either set or reset node switches to low. When M3 and M5 are on, SET node will be discharge through three ...

Switching Regulator

... This document is GStek's confidential information. Anyone having confidential obligation to GStek shall keep this document confidential. Any unauthorized disclosure or use beyond authorized purpose will be considered as violation of confidentiality and criminal and civil liability will be asserted. ...

... This document is GStek's confidential information. Anyone having confidential obligation to GStek shall keep this document confidential. Any unauthorized disclosure or use beyond authorized purpose will be considered as violation of confidentiality and criminal and civil liability will be asserted. ...

You only need to know the filter type (minimum-delay or zero

... Calibration of Digitizers Digitizers normally don’t need to be calibrated if the manufacturer’s specifications are clear and complete. You may want to check the scale factor, normally in microvolts per count, by connecting a battery and a digital voltmeter to the input. Forget about the filter coef ...

... Calibration of Digitizers Digitizers normally don’t need to be calibrated if the manufacturer’s specifications are clear and complete. You may want to check the scale factor, normally in microvolts per count, by connecting a battery and a digital voltmeter to the input. Forget about the filter coef ...

DN190 - Op Amp, Comparator and Reference IC Provides Micropower Monitoring Capability

... supply. The op amp output stage swings from rail-to-rail. Figure 1 lists additional features along with a block diagram of the device. The part’s attributes suggest low power monitoring applications and two such circuits are presented here. Pilot Light Flame Detector with Low-Battery Lockout Figure ...

... supply. The op amp output stage swings from rail-to-rail. Figure 1 lists additional features along with a block diagram of the device. The part’s attributes suggest low power monitoring applications and two such circuits are presented here. Pilot Light Flame Detector with Low-Battery Lockout Figure ...

ad-series-mains-power-supplies

... exchanges, remote antennae sites, ships, oil rigs etc. The units will accept either European 230Vac or US 115Vac inputs and are available as standard in 12V, 24V and 48V output configurations. Input is via a standard IEC-320 C13/14 power cord with UK, European or US mains plugs - please state your r ...

... exchanges, remote antennae sites, ships, oil rigs etc. The units will accept either European 230Vac or US 115Vac inputs and are available as standard in 12V, 24V and 48V output configurations. Input is via a standard IEC-320 C13/14 power cord with UK, European or US mains plugs - please state your r ...

REGULATING PULSE WIDTH MODULATORS

... The SG3525A series of pulse width modulator integrated circuits are designed to offer improved performance and lowered external parts count when used in designing all types of switching power supplies. The on-chip + 5.1 V reference is trimmed to ± 1 % and the input common-mode range of the error amp ...

... The SG3525A series of pulse width modulator integrated circuits are designed to offer improved performance and lowered external parts count when used in designing all types of switching power supplies. The on-chip + 5.1 V reference is trimmed to ± 1 % and the input common-mode range of the error amp ...

File sg2525 | allcomponents.ru

... The SG3525A series of pulse width modulator integrated circuits are designed to offer improved performance and lowered external parts count when used in designing all types of switching power supplies. The on-chip + 5.1 V reference is trimmed to ± 1 % and the input common-mode range of the error amp ...

... The SG3525A series of pulse width modulator integrated circuits are designed to offer improved performance and lowered external parts count when used in designing all types of switching power supplies. The on-chip + 5.1 V reference is trimmed to ± 1 % and the input common-mode range of the error amp ...

Multi Threshold Technique for High Speed and Low Power

... Distributed power gating Simple to implement High area overhead Stack effect can degrade the performance More immune to ground bounce or voltage droop Sleep control signal for maintaining and storing the circuit state ...

... Distributed power gating Simple to implement High area overhead Stack effect can degrade the performance More immune to ground bounce or voltage droop Sleep control signal for maintaining and storing the circuit state ...

Voice of Saturn Voltage Controlled Filter

... Oberheim Xpander. It features two inputs that are summed and then fed into the low-pass filter. The input and output volumes, cutoff frequency and resonance can all be controlled by VC (voltage control) and knobs. One very cool feature of the CEM series filter chips is that as the resonance is turne ...

... Oberheim Xpander. It features two inputs that are summed and then fed into the low-pass filter. The input and output volumes, cutoff frequency and resonance can all be controlled by VC (voltage control) and knobs. One very cool feature of the CEM series filter chips is that as the resonance is turne ...

Helicity Clock Generator - JLab Tech Notes Home Page

... fixed frequency of helicity clock is required in which case the switch should be set to the crystal oscillator lock.2 In this case, there is slow phase slip between line and the outputs. This reference signal is then sent to a phase comparator which controls a voltage controlled oscillator (VCO) whi ...

... fixed frequency of helicity clock is required in which case the switch should be set to the crystal oscillator lock.2 In this case, there is slow phase slip between line and the outputs. This reference signal is then sent to a phase comparator which controls a voltage controlled oscillator (VCO) whi ...

CIRCUIT FUNCTION AND BENEFITS CIRCUIT DESCRIPTION

... reference and is recommended for use with AD7995. A 1 μF decoupling capacitor is recommended on the VIN3/VREF signal for best performance. Care must be taken to ensure that the analog input signal to the ADC does not exceed the supply rails by more than 300 mV. If the signal does exceed this level, ...

... reference and is recommended for use with AD7995. A 1 μF decoupling capacitor is recommended on the VIN3/VREF signal for best performance. Care must be taken to ensure that the analog input signal to the ADC does not exceed the supply rails by more than 300 mV. If the signal does exceed this level, ...

Transistor Switch and Emitter Follower Phys 3610/6610 Lab 18 Student: TA:

... 2.) Let us load this transistor switch with a 10 kΩ resistor to simulate the more realistic situation where your circuit drives some other input. How does the load compare to the output impedance from 1 above? What happens to the output voltage under these load conditions? Would AC coupling between ...

... 2.) Let us load this transistor switch with a 10 kΩ resistor to simulate the more realistic situation where your circuit drives some other input. How does the load compare to the output impedance from 1 above? What happens to the output voltage under these load conditions? Would AC coupling between ...

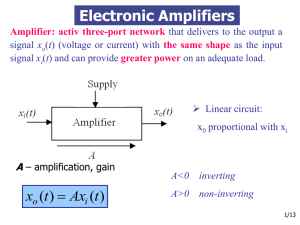

Analog Signal Conditioning

... • it has infinite gain, hence the difference between the input and output voltages is zero. This is denoted by short circuiting the two inputs; V- = V+ • it has zero output impedance, so that the output voltage is independent of the output current. ...

... • it has infinite gain, hence the difference between the input and output voltages is zero. This is denoted by short circuiting the two inputs; V- = V+ • it has zero output impedance, so that the output voltage is independent of the output current. ...

A Reduced Clock-swing Flip-flop (RCSFF) For 63% Power

... is for a data acquisition phase, and the right half shows a precharge phase. It can be seen that the clock goes up only to 2.2 V. In the figure, the data input is assumed to be “high” when the clock is asserted. The solid line path turns on and the node goes down to “low” while remains “high.” and d ...

... is for a data acquisition phase, and the right half shows a precharge phase. It can be seen that the clock goes up only to 2.2 V. In the figure, the data input is assumed to be “high” when the clock is asserted. The solid line path turns on and the node goes down to “low” while remains “high.” and d ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.