Final - Future Archi..

... Figure 2 presents a detailed schematic of the T-gate. The transistors are used as switches for connecting an input signal to the output signal. An input signal appears at the output if the gate voltage of the corresponding transistor goes high. The gate voltage of each transistor is controlled by a ...

... Figure 2 presents a detailed schematic of the T-gate. The transistors are used as switches for connecting an input signal to the output signal. An input signal appears at the output if the gate voltage of the corresponding transistor goes high. The gate voltage of each transistor is controlled by a ...

DC385 - LTC1778EGN Evaluation Kit Quick Start Guide

... valley current control architecture to deliver very low duty cycles without requiring a sense resistor. It provides high efficiency operation at light loads by means of discontinuous mode operation. Noise and RF interference are reduced by means of a forced continuous control pin. The circuit uses a ...

... valley current control architecture to deliver very low duty cycles without requiring a sense resistor. It provides high efficiency operation at light loads by means of discontinuous mode operation. Noise and RF interference are reduced by means of a forced continuous control pin. The circuit uses a ...

g/pdf

... Register File tradeoffs + Very fast (a few gate delays for both read and write) + Adding extra ports is straighporward – Doesn’t scale ...

... Register File tradeoffs + Very fast (a few gate delays for both read and write) + Adding extra ports is straighporward – Doesn’t scale ...

DM74LS74A Dual Positive-Edge-Triggered D Flip

... This device contains two independent positive-edge-triggered D flip-flops with complementary outputs. The information on the D input is accepted by the flip-flops on the positive going edge of the clock pulse. The triggering occurs at a voltage level and is not directly related to the transition tim ...

... This device contains two independent positive-edge-triggered D flip-flops with complementary outputs. The information on the D input is accepted by the flip-flops on the positive going edge of the clock pulse. The triggering occurs at a voltage level and is not directly related to the transition tim ...

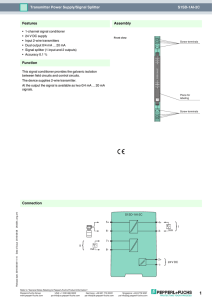

Data Sheet Single Input Dual Output Isolating Amplifier

... The purpose of the RISH CON SI-102 is to electrically isolate input, outputs and power supply. The isolator ful lls all requirements and regulation concerning electromagnetic compatibility EMC and safety (IEC61326-1 and IEC 61010-1:2010). The device has one input and provides two independent outputs ...

... The purpose of the RISH CON SI-102 is to electrically isolate input, outputs and power supply. The isolator ful lls all requirements and regulation concerning electromagnetic compatibility EMC and safety (IEC61326-1 and IEC 61010-1:2010). The device has one input and provides two independent outputs ...

g/plain

... Register File tradeoffs + Very fast (a few gate delays for both read and write) + Adding extra ports is straighporward – Doesn’t scale ...

... Register File tradeoffs + Very fast (a few gate delays for both read and write) + Adding extra ports is straighporward – Doesn’t scale ...

California State University, Fresno Department of Electrical and

... Figure 2: Power supply hook up using the Mastech DC Power Supply The LM747 requires a dual power supply in most applications. A positive voltage with respect to ground is supplied to the V + pins and a negative voltage with respect to ground to the single V − pin. The power supply ground, by itself, ...

... Figure 2: Power supply hook up using the Mastech DC Power Supply The LM747 requires a dual power supply in most applications. A positive voltage with respect to ground is supplied to the V + pins and a negative voltage with respect to ground to the single V − pin. The power supply ground, by itself, ...

exam_01_solution_ake..

... Be sure to justify your answer—answers with no justification get no credit. Solution: 1. The response to the system does not depend on future values of the input, therefore, the system is said to be causal, or non-anticipatory. A few good tips for identifying causality in a system is to look for any ...

... Be sure to justify your answer—answers with no justification get no credit. Solution: 1. The response to the system does not depend on future values of the input, therefore, the system is said to be causal, or non-anticipatory. A few good tips for identifying causality in a system is to look for any ...

Electronic Troubleshooting

... • PR and CLR act like the Set (S) and Reset (R) inputs on a NAND Gate R-S Filip-Flop • Q and Q are always in opposite states • The input CK (clock) on a positive transition causes Q to go either high or low depending on the D input • Q’s state will match the state of D at that time ...

... • PR and CLR act like the Set (S) and Reset (R) inputs on a NAND Gate R-S Filip-Flop • Q and Q are always in opposite states • The input CK (clock) on a positive transition causes Q to go either high or low depending on the D input • Q’s state will match the state of D at that time ...

MDP-1 Brochure 8/01

... DI INPUT: The DI input selects between Instrument (with 10MΩ input impedance at the front 1/4" jack, or 1MΩ at the rear jack) and Line (100KΩ impedance at both inputs, with a -20dB pad ). MIC/DI: Selects between the MIC input (via the XLR input connectors on the rear panel) or DI input signals (via ...

... DI INPUT: The DI input selects between Instrument (with 10MΩ input impedance at the front 1/4" jack, or 1MΩ at the rear jack) and Line (100KΩ impedance at both inputs, with a -20dB pad ). MIC/DI: Selects between the MIC input (via the XLR input connectors on the rear panel) or DI input signals (via ...

Lab1

... Measure the threshold voltages at which a NOT gate switches from Logical “1” to Logical “0” and vice versa. Use Fig. 2 and connect the input of Inverter U1A to a voltage between 0 to +5 V using Agilent Power Supply (0 to +6V but limit it to +5V) or through a potentiometer and the +5V Power supply av ...

... Measure the threshold voltages at which a NOT gate switches from Logical “1” to Logical “0” and vice versa. Use Fig. 2 and connect the input of Inverter U1A to a voltage between 0 to +5 V using Agilent Power Supply (0 to +6V but limit it to +5V) or through a potentiometer and the +5V Power supply av ...

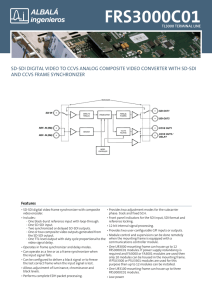

Datasheet - Albalá Ingenieros

... the last correct frame when the input signal is lost. • Allows adjustment of luminance, chrominance and black levels. • Performs complete EDH packet processing. ...

... the last correct frame when the input signal is lost. • Allows adjustment of luminance, chrominance and black levels. • Performs complete EDH packet processing. ...

Clockless Chips - 123SeminarsOnly.com

... working on its worst case execution. •Low speed:-A traditional CPU cannot "go faster" than the expected worst-case performance of the slowest instruction. •High power dissipation:-Clock is a tiny crystal oscillator that keeps vibrating during all time as long as the system is power on, this lead int ...

... working on its worst case execution. •Low speed:-A traditional CPU cannot "go faster" than the expected worst-case performance of the slowest instruction. •High power dissipation:-Clock is a tiny crystal oscillator that keeps vibrating during all time as long as the system is power on, this lead int ...

Op Amp Practice 2 work sheet

... 3. The input impedance of each channel is set by the associated input resistor. The gain of each channel is set by Rf/inputR. Thus, Channel 1: A = -20k/10k = -2, Zin = 10k Channel 2: A = -20k/2k = -10, Zin = 2k Channel 3: A = -20k/5k = -4, Zin = 5k More channels may be added in a similar fashion. No ...

... 3. The input impedance of each channel is set by the associated input resistor. The gain of each channel is set by Rf/inputR. Thus, Channel 1: A = -20k/10k = -2, Zin = 10k Channel 2: A = -20k/2k = -10, Zin = 2k Channel 3: A = -20k/5k = -4, Zin = 5k More channels may be added in a similar fashion. No ...

lab proceedures (word format) - Rose

... • fill out the form as follows: input file: circuitA.cif top cell name: topcell library name: circuitA (assuming this is what you called your library) • repeat for circuitB.cif in the appropriate library, open up topcell - you should see the entire design with pads (you may have to set the number of ...

... • fill out the form as follows: input file: circuitA.cif top cell name: topcell library name: circuitA (assuming this is what you called your library) • repeat for circuitB.cif in the appropriate library, open up topcell - you should see the entire design with pads (you may have to set the number of ...

Class B Output

... Biasing the Class B Output * No DC current is used to bias this configuration. *Activated when the input voltage is greater than the Vbe for the transistors. * npn Transistor operates when positive, pnp when negative. * At a zero input voltage, we get no output voltage. ...

... Biasing the Class B Output * No DC current is used to bias this configuration. *Activated when the input voltage is greater than the Vbe for the transistors. * npn Transistor operates when positive, pnp when negative. * At a zero input voltage, we get no output voltage. ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.