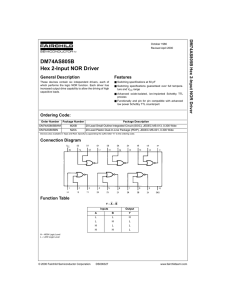

DM74AS805B Hex 2-Input NOR Driver

... 20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide Package Number N20A ...

... 20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide Package Number N20A ...

AD9945 数据手册DataSheet 下载

... CCD’s black level. During the optical black (shielded) pixel interval on each line, the ADC output is compared with the fixed black level reference, selected by the user in the clamp level register. The resulting error signal is filtered to reduce noise, and the correction value is applied to the AD ...

... CCD’s black level. During the optical black (shielded) pixel interval on each line, the ADC output is compared with the fixed black level reference, selected by the user in the clamp level register. The resulting error signal is filtered to reduce noise, and the correction value is applied to the AD ...

Arquitectura de una FPGAs de Xilinx

... – Earlier FPGA architectures require two LUTs per bit to perform the multiplication and addition – The MULT_AND gate enables an area reduction by performing the multiply and the add in one LUT per bit LUT ...

... – Earlier FPGA architectures require two LUTs per bit to perform the multiplication and addition – The MULT_AND gate enables an area reduction by performing the multiply and the add in one LUT per bit LUT ...

ES1869 AudioDrive® Solution Product Brief

... adds 16-bit stereo sound and FM music synthesis to personal computers. It is compliant with the Microsoft® PC 97 and PC 98 specification and WHQL audio requirements. The ES1869 possesses an embedded microcontroller, OPL3TM superset ESFMTM music synthesizer, 16-bit stereo wave ADC and DAC, 16-bit ste ...

... adds 16-bit stereo sound and FM music synthesis to personal computers. It is compliant with the Microsoft® PC 97 and PC 98 specification and WHQL audio requirements. The ES1869 possesses an embedded microcontroller, OPL3TM superset ESFMTM music synthesizer, 16-bit stereo wave ADC and DAC, 16-bit ste ...

Sample-and-Hold Design Eric Sorensen March 16, 2012

... In my first few SHA designs I tried to come up with a filter which could selectively filter out the input signal at the hold capacitor node [Razavi]. This filter inevitably loaded down the node too much and caused problems with droop. In this topology an equal-and-opposite signal is injected into th ...

... In my first few SHA designs I tried to come up with a filter which could selectively filter out the input signal at the hold capacitor node [Razavi]. This filter inevitably loaded down the node too much and caused problems with droop. In this topology an equal-and-opposite signal is injected into th ...

v 2 - EngineeringDuniya.com

... Magnitudes of both may be same The other terminal of both power supplies are connected to common ground All input and output voltages are measured with reference to the common ground ...

... Magnitudes of both may be same The other terminal of both power supplies are connected to common ground All input and output voltages are measured with reference to the common ground ...

EELab2_Exp2_AD_Converter_V3 720KB Apr 18 2016 08:18:48

... which are usually continuous voltages or currents, to digital words used in computing, data transmission, information processing and storage, and control systems. We do this conversion because digital signals are easy to store, debug, and are almost free from noise. ...

... which are usually continuous voltages or currents, to digital words used in computing, data transmission, information processing and storage, and control systems. We do this conversion because digital signals are easy to store, debug, and are almost free from noise. ...

HMC959LC3 - uri=media.digikey

... pin forces the Q output low regardless of the clock edge state (asynchronous reset assertion). Reversing the clock inputs allows for negative-edge triggered applications. All differential inputs to the HMC959LC3 are CML and terminated on-chip with 50 Ohms to the positive supply, GND, and may be DC o ...

... pin forces the Q output low regardless of the clock edge state (asynchronous reset assertion). Reversing the clock inputs allows for negative-edge triggered applications. All differential inputs to the HMC959LC3 are CML and terminated on-chip with 50 Ohms to the positive supply, GND, and may be DC o ...

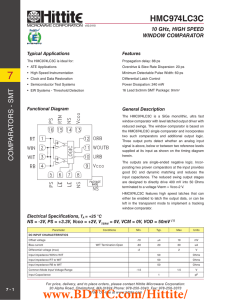

HMC974LC3C 数据资料DataSheet下载

... two such comparators and additional output logic. Three output ports detect whether an analog input signal is above, below or between two reference levels supplied at its input as shown on the timing diagram herein. The outputs are single-ended negative logic. Incorporating two proven comparators at ...

... two such comparators and additional output logic. Three output ports detect whether an analog input signal is above, below or between two reference levels supplied at its input as shown on the timing diagram herein. The outputs are single-ended negative logic. Incorporating two proven comparators at ...

Low-Voltage CMOS Analog Bootstrapped Switch For

... Most analog-to-digital converters (ADC) typically employ a sample-and-hold circuit at the front end that must achieve high speed, high linearity and high precision with low-power dissipation. In low-voltage systems, analog sampling becomes particularly difficult because the limited headroom severely ...

... Most analog-to-digital converters (ADC) typically employ a sample-and-hold circuit at the front end that must achieve high speed, high linearity and high precision with low-power dissipation. In low-voltage systems, analog sampling becomes particularly difficult because the limited headroom severely ...

ICS251 - Integrated Device Technology

... Connect this to Ground. Powers down entire chip. Tri-states CLK outputs when low. No internal pull-up resistor. The pin must be tied either directly or through the external resistor to VDD or GND. External resistor value must be less than 15kOhm. ...

... Connect this to Ground. Powers down entire chip. Tri-states CLK outputs when low. No internal pull-up resistor. The pin must be tied either directly or through the external resistor to VDD or GND. External resistor value must be less than 15kOhm. ...

CML Semiconductor Products

... the carrier detect time constant is set by an external capacitor, whose value should be arranged as required to further enhance this product's performance in high noise environments. This low-power device requires few external components and is available in small outline plastic (S.O.I.C) and cerdip ...

... the carrier detect time constant is set by an external capacitor, whose value should be arranged as required to further enhance this product's performance in high noise environments. This low-power device requires few external components and is available in small outline plastic (S.O.I.C) and cerdip ...

Low power quad voltage comparator

... 3. The input common-mode voltage of either input signal voltage should not be allowed to go negative by more than 0.3V. The upper end of the common-mode voltage range is VCC+ –1.5V, but either or both inputs can go to +30V without damage. 4. The response time specified is for a 100mV input step with ...

... 3. The input common-mode voltage of either input signal voltage should not be allowed to go negative by more than 0.3V. The upper end of the common-mode voltage range is VCC+ –1.5V, but either or both inputs can go to +30V without damage. 4. The response time specified is for a 100mV input step with ...

6. Typical discrete input and output devices

... If the contact of the field input device is closed (SS=1), the indicator neon lamp is lit. The optocoupler LED is lit by a rectified sinusoidal current from the diode bridge. Consequently, the optocoupler phototransistor remains in saturation most of the time. Its collector voltage stays low continu ...

... If the contact of the field input device is closed (SS=1), the indicator neon lamp is lit. The optocoupler LED is lit by a rectified sinusoidal current from the diode bridge. Consequently, the optocoupler phototransistor remains in saturation most of the time. Its collector voltage stays low continu ...

CAT4016 - LED Driver, 16-Channel, Constant Current

... currents are programmed together via an external RSET resistor. Low output voltage operation on the LED channels as low as 0.4 V (for 2 to 100 mA LED current) allows for more power efficient designs. A high−speed 4−wire serial interface of up to 25 MHz clock frequency controls each individual channe ...

... currents are programmed together via an external RSET resistor. Low output voltage operation on the LED channels as low as 0.4 V (for 2 to 100 mA LED current) allows for more power efficient designs. A high−speed 4−wire serial interface of up to 25 MHz clock frequency controls each individual channe ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.