The DatasheetArchive - Datasheet Search Engine

... Note 1: ‘‘Absolute Maximum Ratings’’ are those values beyond which the safety of the device cannot be guaranteed. Except for ‘‘Operating Temperature Range’’ they are not meant to imply that the devices should be operated at these limits. The table of ‘‘Electrical Characteristics’’ provides condition ...

... Note 1: ‘‘Absolute Maximum Ratings’’ are those values beyond which the safety of the device cannot be guaranteed. Except for ‘‘Operating Temperature Range’’ they are not meant to imply that the devices should be operated at these limits. The table of ‘‘Electrical Characteristics’’ provides condition ...

CAT4016 - LED Driver, 16-Channel, Constant Current

... currents are programmed together via an external RSET resistor. Low output voltage operation on the LED channels as low as 0.4 V (for 2 to 100 mA LED current) allows for more power efficient designs. A high−speed 4−wire serial interface of up to 25 MHz clock frequency controls each individual channe ...

... currents are programmed together via an external RSET resistor. Low output voltage operation on the LED channels as low as 0.4 V (for 2 to 100 mA LED current) allows for more power efficient designs. A high−speed 4−wire serial interface of up to 25 MHz clock frequency controls each individual channe ...

Si52131-A11A - Silicon Labs

... pin needs to be logic low and the I2C output enable bit needs to be logic high. By default, the OE pin is set to a logic low and the I2C output enable bit is set to a logic high. There are two methods to disable the output clock: the OE pin is pulled to a logic high or the I2C output enable bit is s ...

... pin needs to be logic low and the I2C output enable bit needs to be logic high. By default, the OE pin is set to a logic low and the I2C output enable bit is set to a logic high. There are two methods to disable the output clock: the OE pin is pulled to a logic high or the I2C output enable bit is s ...

NC7WB3125 2-Bit Low Power Bus Switch N C

... The NC7WB3125 is a 2-bit ultra high-speed CMOS FET bus switch with TTL-compatible active LOW control inputs. The low On Resistance of the switch allows inputs to be connected to outputs with minimal propagation delay and without generating additional ground bounce noise. The device is organized as a ...

... The NC7WB3125 is a 2-bit ultra high-speed CMOS FET bus switch with TTL-compatible active LOW control inputs. The low On Resistance of the switch allows inputs to be connected to outputs with minimal propagation delay and without generating additional ground bounce noise. The device is organized as a ...

P10

... voltage of its own, and is modeled by a resistive element Ri called the input resistance. The output port is modeled by a dependent voltage source AVi in series with the output resistance R0, where Vi is the potential difference between the input port terminals. Picture 1 shows a complete amplifier ...

... voltage of its own, and is modeled by a resistive element Ri called the input resistance. The output port is modeled by a dependent voltage source AVi in series with the output resistance R0, where Vi is the potential difference between the input port terminals. Picture 1 shows a complete amplifier ...

Series Catalog Page

... INHIBIT signal The INHIBIT signal is used to turn the power supply ON and OFF. TTL “1”or OPEN – will turn on the power supply. (For normal operation leave the signal not connected.) TTL “0” – will turn off the power supply. SYNC IN signal The SYNC IN signal is used to allow the power supply frequenc ...

... INHIBIT signal The INHIBIT signal is used to turn the power supply ON and OFF. TTL “1”or OPEN – will turn on the power supply. (For normal operation leave the signal not connected.) TTL “0” – will turn off the power supply. SYNC IN signal The SYNC IN signal is used to allow the power supply frequenc ...

Action PAK AP4351 ® Thermocouple-Input,

... The AP4351 isolating thermocouple conditioner offers wide ranging input and output capability. The AP4351 can be field configured by the user to accept input from thermocouple types J, K, T, R, S, E, and B and to provide current or voltage output. The output is linearized to temperature according to ...

... The AP4351 isolating thermocouple conditioner offers wide ranging input and output capability. The AP4351 can be field configured by the user to accept input from thermocouple types J, K, T, R, S, E, and B and to provide current or voltage output. The output is linearized to temperature according to ...

Test Procedure for the NCV8853GEVB Evaluation Board

... 1. The Power Good pin (PG) allows you to digitally monitor the output voltage. When above 90% of the expected value, the PG signal is in a high state. By default, it is pulled high to VOUT through a 10kΩ resistor. 2. Optional: To pull the PG pin high using a signal other than VOUT, please make the f ...

... 1. The Power Good pin (PG) allows you to digitally monitor the output voltage. When above 90% of the expected value, the PG signal is in a high state. By default, it is pulled high to VOUT through a 10kΩ resistor. 2. Optional: To pull the PG pin high using a signal other than VOUT, please make the f ...

Analog Lock-In Amplifiers - Stanford Research Systems

... filter frequency, demodulator phase shift, and source output amplitude. The drive electronics are completely static, with no “scanning” or refresh to generate the slightest interference. Whenever the microcontroller becomes active, the “CPU Activity” indicator illuminates, clearly showing when the d ...

... filter frequency, demodulator phase shift, and source output amplitude. The drive electronics are completely static, with no “scanning” or refresh to generate the slightest interference. Whenever the microcontroller becomes active, the “CPU Activity” indicator illuminates, clearly showing when the d ...

isscc 2012 / session 18 / innovative circuits in

... stages) will discharge the 106pF capacitor less as compared to the logic zero (75% active high on after 3 inverter stages) and hence a different signal is stored in the D-Flip-Flop at the next falling edge of the incoming signal. Two different 4bit input decoders (code A=0010, code B=0110) and two d ...

... stages) will discharge the 106pF capacitor less as compared to the logic zero (75% active high on after 3 inverter stages) and hence a different signal is stored in the D-Flip-Flop at the next falling edge of the incoming signal. Two different 4bit input decoders (code A=0010, code B=0110) and two d ...

the General SKRM-C8 Data Sheet

... The SKRM-C8-XXX is a tiny daughter card that can be installed on the main board of products such as guitar amplifiers, PAs and mixers. The module features stereo analog inputs, stereo analog outputs, three control voltage inputs for parameter adjustment and three digital inputs for program selection ...

... The SKRM-C8-XXX is a tiny daughter card that can be installed on the main board of products such as guitar amplifiers, PAs and mixers. The module features stereo analog inputs, stereo analog outputs, three control voltage inputs for parameter adjustment and three digital inputs for program selection ...

Abstract.

... the 100MHz clock on the CMOS counter clock in the close vicinity of the high sensitive front-end. Even at very low threshold no significant crosstalk at the output of the ...

... the 100MHz clock on the CMOS counter clock in the close vicinity of the high sensitive front-end. Even at very low threshold no significant crosstalk at the output of the ...

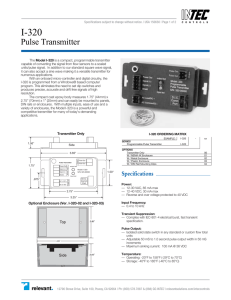

Pulse Transmitter

... 2. “K” and Offset values - manually entered from values in sensor operators manual or automatically entered using the auto button. 3. Units per output pulse 4. Filter setting 5. Pulse width Once the values are set, the “send” command loads the transmitter. All programming can be saved with a file na ...

... 2. “K” and Offset values - manually entered from values in sensor operators manual or automatically entered using the auto button. 3. Units per output pulse 4. Filter setting 5. Pulse width Once the values are set, the “send” command loads the transmitter. All programming can be saved with a file na ...

LED level meter driver, 12-point 2 channel, VU scale, bar display

... (see Fig. 5). One complete cycle of the timing chart starting from O1 (pin 21) is as follows: if the channel 1 input is higher than comparator level 1 during the first-point period for channel 1, a “L” level is output. Next, if the channel 1 input is higher than comparator level 2 during the second- ...

... (see Fig. 5). One complete cycle of the timing chart starting from O1 (pin 21) is as follows: if the channel 1 input is higher than comparator level 1 during the first-point period for channel 1, a “L” level is output. Next, if the channel 1 input is higher than comparator level 2 during the second- ...

LT1711/LT1712 - Single/Dual 4.5ns, 3V/5V/±5V, Rail-to-Rail Comparators

... differential input stage, the LT1711/LT1712 bias current flows into or out of the device depending upon the common mode level. The input circuit consists of an NPN pair and a PNP pair. For inputs near the negative rail, the NPN pair is inactive, and the input bias current flows out of the device; fo ...

... differential input stage, the LT1711/LT1712 bias current flows into or out of the device depending upon the common mode level. The input circuit consists of an NPN pair and a PNP pair. For inputs near the negative rail, the NPN pair is inactive, and the input bias current flows out of the device; fo ...

Sequential Circuit Design

... Delay Locked Loop (DLL) • It is a variant of PLL that uses voltage-controlled delay ...

... Delay Locked Loop (DLL) • It is a variant of PLL that uses voltage-controlled delay ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.