SA604A High performance low power FM IF system Philips Semiconductors

... shown in Figure 3. This configuration can be used as the basis for production layout. ...

... shown in Figure 3. This configuration can be used as the basis for production layout. ...

Diode Logic

... In this figure, if both inputs are left unconnected or are both at logic 0, output Z will also be held at zero volts by the resistor, and will thus be a logic 0 as well. However, if either input is raised to +5 volts, its diode will become forward biased and will therefore conduct. This in turn will ...

... In this figure, if both inputs are left unconnected or are both at logic 0, output Z will also be held at zero volts by the resistor, and will thus be a logic 0 as well. However, if either input is raised to +5 volts, its diode will become forward biased and will therefore conduct. This in turn will ...

AD781

... Designers of data conversion circuits must also consider the effect of noise sources on the accuracy of the data acquisition system. A sample-and-hold amplifier that precedes the A-to-D converter introduces some noise and represents another source of uncertainty in the conversion process. The noise ...

... Designers of data conversion circuits must also consider the effect of noise sources on the accuracy of the data acquisition system. A sample-and-hold amplifier that precedes the A-to-D converter introduces some noise and represents another source of uncertainty in the conversion process. The noise ...

OT 110/120…277/1A4 2DIMLT2 P

... input voltage of the load is within the declared output voltage range of the driver. In all other cases the driver may shut down the load. _ The driver may shut down in case no load is connected to the driver output until the correct load is connected and a power off/on cycle is performed. Hot-plug ...

... input voltage of the load is within the declared output voltage range of the driver. In all other cases the driver may shut down the load. _ The driver may shut down in case no load is connected to the driver output until the correct load is connected and a power off/on cycle is performed. Hot-plug ...

F04_PotTach_L09

... In addition to providing angular position, potentiometers can be used to measure angular velocity using an external op-amp circuit like the one shown in Figure 1. The first stage of the circuit buffers the output of the potentiometer so as not to draw current from the wiper of the potentiometer. Th ...

... In addition to providing angular position, potentiometers can be used to measure angular velocity using an external op-amp circuit like the one shown in Figure 1. The first stage of the circuit buffers the output of the potentiometer so as not to draw current from the wiper of the potentiometer. Th ...

AD8561 Data Sheet

... the input common-mode range to extend all the way from the negative supply rail to within 2.2 V of the positive supply rail. The input common-mode voltage can be found as the average of the voltage at the two inputs of the device. To ensure the fastest response time, care should be taken not to allo ...

... the input common-mode range to extend all the way from the negative supply rail to within 2.2 V of the positive supply rail. The input common-mode voltage can be found as the average of the voltage at the two inputs of the device. To ensure the fastest response time, care should be taken not to allo ...

MPU/0 Instructions(Word)

... operator in the opposite direction to its last cycle. If a START or SAFETY input is received during the closing cycle the operators will stop and automatically re-open. If a START input is received during the open cycle the operators stop, the next input run the operators closed. SAFETY inputs are i ...

... operator in the opposite direction to its last cycle. If a START or SAFETY input is received during the closing cycle the operators will stop and automatically re-open. If a START input is received during the open cycle the operators stop, the next input run the operators closed. SAFETY inputs are i ...

installer`s reference .............. xtant 302a

... ports dedicated to the amplifier are labeled Amp Vert/Horiz Acc. Port and Amp Vert. Acc. Port. The third port is dedicated to the RCA line outputs and is labeled Line Out Vert. Acc. Port. Xtant offers two types of accessory modules which are designed for either “Horizontal” or “Vertical” mounting. T ...

... ports dedicated to the amplifier are labeled Amp Vert/Horiz Acc. Port and Amp Vert. Acc. Port. The third port is dedicated to the RCA line outputs and is labeled Line Out Vert. Acc. Port. Xtant offers two types of accessory modules which are designed for either “Horizontal” or “Vertical” mounting. T ...

IOSR Journal of Electronics and Communication Engineering (IOSR-JECE)

... connected to power distribution amplifier, and the signal distributed onto two lines. The first line enters the data processor, and the second line enters the clock regenerator in receiver. Before entering the data processor in receiver, demodulation process of AM signal yields data signal. The sign ...

... connected to power distribution amplifier, and the signal distributed onto two lines. The first line enters the data processor, and the second line enters the clock regenerator in receiver. Before entering the data processor in receiver, demodulation process of AM signal yields data signal. The sign ...

AD8561 数据手册DataSheet 下载

... the input common-mode range to extend all the way from the negative supply rail to within 2.2 V of the positive supply rail. The input common-mode voltage can be found as the average of the voltage at the two inputs of the device. To ensure the fastest response time, care should be taken not to allo ...

... the input common-mode range to extend all the way from the negative supply rail to within 2.2 V of the positive supply rail. The input common-mode voltage can be found as the average of the voltage at the two inputs of the device. To ensure the fastest response time, care should be taken not to allo ...

12-Bit, 80 MSPS CommsADC? Analog-to-Digital

... mode of the clock inputs is set internally to AVDD/2 using 5-kΩ resistors (Figure 20). The clock input should be either a sine wave or a square wave having a 50% duty cycle. When driven with a single-ended CMOS clock input, it is best to connect the CLK input to ground with a 0.01-µF capacitor (see ...

... mode of the clock inputs is set internally to AVDD/2 using 5-kΩ resistors (Figure 20). The clock input should be either a sine wave or a square wave having a 50% duty cycle. When driven with a single-ended CMOS clock input, it is best to connect the CLK input to ground with a 0.01-µF capacitor (see ...

Theory of Operations - University of Portland

... resistors and a parallel capacitor. They are commonly referred to as a charge pump because voltage is constantly being pumped into and out of the capacitor. When the incoming signal from the PFD is logic high, the capacitor charges up, increasing the output control voltage. When the incoming signal ...

... resistors and a parallel capacitor. They are commonly referred to as a charge pump because voltage is constantly being pumped into and out of the capacitor. When the incoming signal from the PFD is logic high, the capacitor charges up, increasing the output control voltage. When the incoming signal ...

Appendix N - Assistive Listening Systems Performance Standards

... being considered for a different induction loop system and produces an average magnetic field strength exceeding 15 mA/meter, then it is recommended that, unless the use of each system can be scheduled so as not to occur simultaneously, an induction loop system not be considered in the new area. 3. ...

... being considered for a different induction loop system and produces an average magnetic field strength exceeding 15 mA/meter, then it is recommended that, unless the use of each system can be scheduled so as not to occur simultaneously, an induction loop system not be considered in the new area. 3. ...

Topic 4: Digital Circuits

... • Very little (0(nA)) current in output chain, except during switching when both transistors are partially on • More power required when signal rise times are small since transistors are on longer • Symmetric output structure ==> equally strong drive (IOH, IOL) in LOW and HIGH states ...

... • Very little (0(nA)) current in output chain, except during switching when both transistors are partially on • More power required when signal rise times are small since transistors are on longer • Symmetric output structure ==> equally strong drive (IOH, IOL) in LOW and HIGH states ...

Analog Path Amplification/Attenuation Resistive divider --

... Figure 10 shows the input and output of the filter. The yellow curve is the input to the filter and the red curve is the output of the filter. There is some time delay between the input and output of the filter but it is in the µs range. The Input signal was changed and for all signals with a freque ...

... Figure 10 shows the input and output of the filter. The yellow curve is the input to the filter and the red curve is the output of the filter. There is some time delay between the input and output of the filter but it is in the µs range. The Input signal was changed and for all signals with a freque ...

DC786 - LTC4260CGN Evaluation Kit Quick Start Guide

... to an I2C bus. Power for D4-7 is supplied by JP7, so in this mode the LEDs will not light. Setting JP3 SDA to COM connects SDAO and SDAI together for communication to a non-isolated bus. Splitting SDAO and SDAI facilitates optically isolated applications (see the LTC4260 data sheet). The I2C address ...

... to an I2C bus. Power for D4-7 is supplied by JP7, so in this mode the LEDs will not light. Setting JP3 SDA to COM connects SDAO and SDAI together for communication to a non-isolated bus. Splitting SDAO and SDAI facilitates optically isolated applications (see the LTC4260 data sheet). The I2C address ...

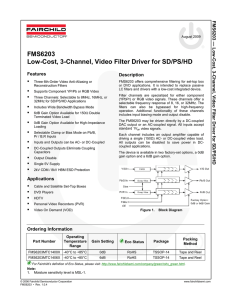

FMS6203 Low-Cost, 3-Channel, Video Filter Driver for SD/PS/HD FM S6203 — Low-

... pin as possible. This greatly reduces the parasitic capacitance and inductance effect on the FMS6203 output driver. Recommended distance from device pin to place series termination resistor is no greater than 0.1 inches. ...

... pin as possible. This greatly reduces the parasitic capacitance and inductance effect on the FMS6203 output driver. Recommended distance from device pin to place series termination resistor is no greater than 0.1 inches. ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.