MAX196/MAX198 Multirange, Single +5V, 12-Bit DAS with 12-Bit Bus Interface _______________General Description

... The MAX196/MAX198 multirange, 12-bit data-acquisition systems (DAS) require only a single +5V supply for operation, yet convert analog signals at their inputs up to ±10V (MAX196) and ±4V (MAX198). These systems provide six analog input channels that are independently software programmable for a vari ...

... The MAX196/MAX198 multirange, 12-bit data-acquisition systems (DAS) require only a single +5V supply for operation, yet convert analog signals at their inputs up to ±10V (MAX196) and ±4V (MAX198). These systems provide six analog input channels that are independently software programmable for a vari ...

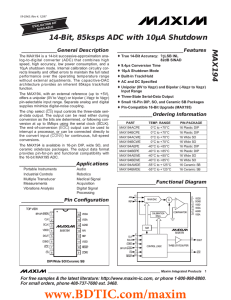

MAX194 14-Bit, 85ksps ADC with 10µA Shutdown _______________General Description ____________________________Features

... of CONV must occur during the period shown in Figures 3 and 4. When CLK is not directly controlled by your processor, two methods of ensuring synchronization are to drive CONV from EOC (continuous conversions) or to gate the conversion-start signal with the conversion clock so that CONV can go low o ...

... of CONV must occur during the period shown in Figures 3 and 4. When CLK is not directly controlled by your processor, two methods of ensuring synchronization are to drive CONV from EOC (continuous conversions) or to gate the conversion-start signal with the conversion clock so that CONV can go low o ...

MAX187/MAX189 +5V, Low-Power, 12

... devices accept external reference voltages from +2.5V to VDD. The serial interface requires only three digital lines, SCLK, CS, and DOUT, and provides easy interface to microprocessors (µPs). Both converters have two modes: normal and shutdown. Pulling SHDN low shuts the device down and reduces supp ...

... devices accept external reference voltages from +2.5V to VDD. The serial interface requires only three digital lines, SCLK, CS, and DOUT, and provides easy interface to microprocessors (µPs). Both converters have two modes: normal and shutdown. Pulling SHDN low shuts the device down and reduces supp ...

MAX3346E ±15kV ESD-Protected USB Transceiver in UCSP General Description

... than 40µA. In this mode, RCV is forced low, and D+ and D- are high-impedance inputs (Table 3d). In suspend mode, data can only be transmitted with full-speed slope control. SPEED SPEED is a control input that selects between low-speed (1.5Mbps) and full-speed (12Mbps) USB transmission. Internally, i ...

... than 40µA. In this mode, RCV is forced low, and D+ and D- are high-impedance inputs (Table 3d). In suspend mode, data can only be transmitted with full-speed slope control. SPEED SPEED is a control input that selects between low-speed (1.5Mbps) and full-speed (12Mbps) USB transmission. Internally, i ...

286 New data bus systems – LIN, MOST, Bluetooth Self

... The synch field consists of the bit sequence 0 1 0 1 0 1 0 1 0 1. This bit sequence enables all LIN slave control units to adapt to (become synchronised with) the system clock of the LIN master control unit. The synchronisation of all control units is essential to proper data exchange. Without synch ...

... The synch field consists of the bit sequence 0 1 0 1 0 1 0 1 0 1. This bit sequence enables all LIN slave control units to adapt to (become synchronised with) the system clock of the LIN master control unit. The synchronisation of all control units is essential to proper data exchange. Without synch ...

mae511

... flip-flop, for which the data input is Q1 . The output of the second flip-flop, denoted Q2 , is a signal which is low for 6 ADC clock periods, high (+5 V) for the next 18, and then low again for the next 24, and repeats. Note that we refer to Q1 and Q2 as the outputs of the first and second D-type f ...

... flip-flop, for which the data input is Q1 . The output of the second flip-flop, denoted Q2 , is a signal which is low for 6 ADC clock periods, high (+5 V) for the next 18, and then low again for the next 24, and repeats. Note that we refer to Q1 and Q2 as the outputs of the first and second D-type f ...

AD9753 数据手册DataSheet 下载

... The AD9753 has been optimized for ultrahigh speed applications up to 300 MSPS where data rates exceed those possible on a single data interface port DAC. The digital interface consists of two buffered latches as well as control logic. These latches can be time multiplexed to the high speed DAC in se ...

... The AD9753 has been optimized for ultrahigh speed applications up to 300 MSPS where data rates exceed those possible on a single data interface port DAC. The digital interface consists of two buffered latches as well as control logic. These latches can be time multiplexed to the high speed DAC in se ...

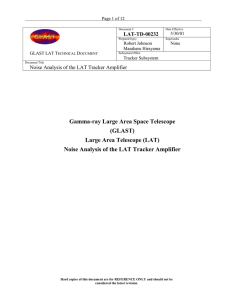

1 Abstract - glast lat

... Simulated shaper output pulses for two bias configurations and 0.1 fC input charge, compared with an ideal RC/CR pulse. The ENC results shown in Table 1 can be misleading (suggesting more S/N than is really there), because they do not take into account the fact that the gain increases significantly ...

... Simulated shaper output pulses for two bias configurations and 0.1 fC input charge, compared with an ideal RC/CR pulse. The ENC results shown in Table 1 can be misleading (suggesting more S/N than is really there), because they do not take into account the fact that the gain increases significantly ...

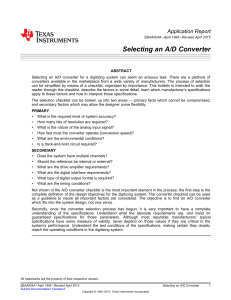

Selecting an A/D Converter (Rev. A)

... of integral nonlinearity referred to end points and Figure 6 is an example of integral nonlinearity referred to the best-fit line. For the end point linearity, a straight line is drawn between the converter’s offset and gain intercept points, the transfer function is plotted against that straight li ...

... of integral nonlinearity referred to end points and Figure 6 is an example of integral nonlinearity referred to the best-fit line. For the end point linearity, a straight line is drawn between the converter’s offset and gain intercept points, the transfer function is plotted against that straight li ...

MAX3748 Compact 155Mbps to 4.25Gbps Limiting Amplifier General Description

... Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Expo ...

... Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Expo ...

MAX196,198 - Part Number Search

... the MAX198. This range switching increases the effective dynamic range to 14 bits and provides the flexibility to interface ±12V, ±15V, and 4mA to 20mA powered sensors to a single +5V system. In addition, these converters are fault protected to ±16.5V; a fault condition on any channel will not affec ...

... the MAX198. This range switching increases the effective dynamic range to 14 bits and provides the flexibility to interface ±12V, ±15V, and 4mA to 20mA powered sensors to a single +5V system. In addition, these converters are fault protected to ±16.5V; a fault condition on any channel will not affec ...

MAX1005 IF Undersampler _______________General Description ____________________________Features

... The MAX1005 is a combined digitizer and reconstruction integrated circuit designed to work in systems that demodulate and modulate communications signals. It integrates IF undersampling and signal synthesis functions into a single, low-power circuit. Its analog-todigital converter (ADC) is used to d ...

... The MAX1005 is a combined digitizer and reconstruction integrated circuit designed to work in systems that demodulate and modulate communications signals. It integrates IF undersampling and signal synthesis functions into a single, low-power circuit. Its analog-todigital converter (ADC) is used to d ...

technical data - Blakley Electrics

... system is purely single phaseTECHNICAL or whether it is a single phaseTECHNICAL supply derived from two TECHNICAL TECHNICAL DATA DATA DATA poles of a three phase system. For three phase circuits, because the star point is never taken out to provide a neutral conductor, triple pole MCBsTECHNICAL are ...

... system is purely single phaseTECHNICAL or whether it is a single phaseTECHNICAL supply derived from two TECHNICAL TECHNICAL DATA DATA DATA poles of a three phase system. For three phase circuits, because the star point is never taken out to provide a neutral conductor, triple pole MCBsTECHNICAL are ...

LAB-2 (Tutorial) Simulation of LNA (Cadence

... the load divided by the power available from the source. This gain definition is the same as that for GP. Therefore, the gain from PSS should match GP when the input power level is low and nonlinearity is weak. In case of differential LNA the even mode disturbances will be suppressed. Electrical Eng ...

... the load divided by the power available from the source. This gain definition is the same as that for GP. Therefore, the gain from PSS should match GP when the input power level is low and nonlinearity is weak. In case of differential LNA the even mode disturbances will be suppressed. Electrical Eng ...

LMH0394 - Texas Instruments

... improved immunity to crosstalk and ultra low power consumption. The equalizer includes active sensing circuitry that ensures robust performance and enhanced immunity to variations in the input signal launch amplitude. The output driver offers programmable de-emphasis for up to 40” of FR4 trace losse ...

... improved immunity to crosstalk and ultra low power consumption. The equalizer includes active sensing circuitry that ensures robust performance and enhanced immunity to variations in the input signal launch amplitude. The output driver offers programmable de-emphasis for up to 40” of FR4 trace losse ...

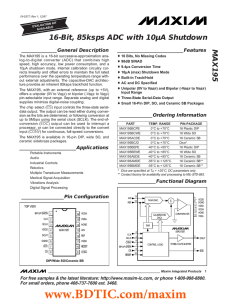

MAX195 16-Bit, 85ksps ADC with 10µA Shutdown _______________General Description ____________________________Features

... period shown in Figures 3 and 4. When CLK is not directly controlled by your processor, two methods of ensuring synchronization are to drive CONV from EOC (continuous conversions) or to gate the conversion-start signal with the conversion clock so that CONV can go low only while CLK is low (Figure 5 ...

... period shown in Figures 3 and 4. When CLK is not directly controlled by your processor, two methods of ensuring synchronization are to drive CONV from EOC (continuous conversions) or to gate the conversion-start signal with the conversion clock so that CONV can go low only while CLK is low (Figure 5 ...

Package `crqa`

... delay indicated than the another, the function selects the longer delay of the two to ensure that new information is gained for both. When the delays are close to each other, the function computes the mean of the two delays. 2) Determine embedding dimensions by using false nearest neighbors and chec ...

... delay indicated than the another, the function selects the longer delay of the two to ensure that new information is gained for both. When the delays are close to each other, the function computes the mean of the two delays. 2) Determine embedding dimensions by using false nearest neighbors and chec ...

MAX1144/MAX1145 14-Bit ADCs, 150ksps, 3.3V Single Supply General Description Features

... To minimize linearity, offset, and gain errors, the MAX1144/MAX1145 have on-demand software calibration. Initiate calibration by writing a control byte with bit M1 = 0 and bit M0 = 1 (Table 1). Select internal or external clock for calibration by setting the INT/EXT bit in the control byte. Calibrat ...

... To minimize linearity, offset, and gain errors, the MAX1144/MAX1145 have on-demand software calibration. Initiate calibration by writing a control byte with bit M1 = 0 and bit M0 = 1 (Table 1). Select internal or external clock for calibration by setting the INT/EXT bit in the control byte. Calibrat ...

LSK489 Applica on Note

... current and input noise current. This arrangement has the disadvantage that the input noise of the op amp adds to that of the JFETs. In (b) a JFET differen al pair with a gain of 10X is placed in front of the op amp. The gain of the JFET stage swamps out the noise contribu on of the op amp and increa ...

... current and input noise current. This arrangement has the disadvantage that the input noise of the op amp adds to that of the JFETs. In (b) a JFET differen al pair with a gain of 10X is placed in front of the op amp. The gain of the JFET stage swamps out the noise contribu on of the op amp and increa ...

FM25V05, 512-Kbit (64 K × 8) Serial (SPI) F-RAM

... may share the SI and SO lines as described earlier. The FM25V05 has two separate pins for SI and SO, which can be connected with the master as shown in Figure 2. For a microcontroller that has no dedicated SPI bus, a general-purpose port may be used. To reduce hardware ...

... may share the SI and SO lines as described earlier. The FM25V05 has two separate pins for SI and SO, which can be connected with the master as shown in Figure 2. For a microcontroller that has no dedicated SPI bus, a general-purpose port may be used. To reduce hardware ...

GTL2034PW

... Stresses beyond those listed may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under Section 9 “Recommended operating conditions” is not implied. Exposure to absolute-maximum-rated co ...

... Stresses beyond those listed may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under Section 9 “Recommended operating conditions” is not implied. Exposure to absolute-maximum-rated co ...

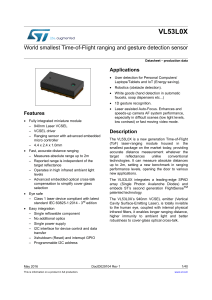

World smallest Time-of-Flight ranging and gesture detection sensor

... System functional description Figure 4 shows the system level functional description. The host customer application is controlling the VL53L0X device using an API (Application Programming Interface). The API is exposing to the customer application a set of high level functions that allows control of ...

... System functional description Figure 4 shows the system level functional description. The host customer application is controlling the VL53L0X device using an API (Application Programming Interface). The API is exposing to the customer application a set of high level functions that allows control of ...

AR0132AT 1/3-Inch CMOS Digital Image

... analog signal chain (providing offset correction and gain), and then through an analogto-digital converter (ADC). The output from the ADC is a 12-bit value for each pixel in the array. The ADC output passes through a digital processing signal chain (which provides further data path corrections and a ...

... analog signal chain (providing offset correction and gain), and then through an analogto-digital converter (ADC). The output from the ADC is a 12-bit value for each pixel in the array. The ADC output passes through a digital processing signal chain (which provides further data path corrections and a ...