DR230 Hybrid Recorder

... as temperature, flow rate, strain, etc. and can simultaneously record and transfer the measured data to a personal computer or store it in a memory device (floppy disk). The DR230 is available in two versions, a stand-alone model which has an integrated input, output and recording section and a maxi ...

... as temperature, flow rate, strain, etc. and can simultaneously record and transfer the measured data to a personal computer or store it in a memory device (floppy disk). The DR230 is available in two versions, a stand-alone model which has an integrated input, output and recording section and a maxi ...

USB3290 Small Footprint Hi-Speed USB 2.0 Device PHY with UTMI

... reserves the right to make changes to specifications and product descriptions at any time without notice. Contact your local SMSC sales office to obtain the latest specifications before placing your product order. The provision of this information does not convey to the purchaser of the described se ...

... reserves the right to make changes to specifications and product descriptions at any time without notice. Contact your local SMSC sales office to obtain the latest specifications before placing your product order. The provision of this information does not convey to the purchaser of the described se ...

- Free Documents

... scan Low power fps VGA progressive scan ITUR BT. YUV YCbCr with embedded syncs, YUV YCbCr , RGB , RGB , Bayer bit or Bayer bit output formats bit parallel video interface, horizontal and vertical syncs, MHz max clock Twowire serial control interface Onchip PLL, . to MHz clock input Analog power supp ...

... scan Low power fps VGA progressive scan ITUR BT. YUV YCbCr with embedded syncs, YUV YCbCr , RGB , RGB , Bayer bit or Bayer bit output formats bit parallel video interface, horizontal and vertical syncs, MHz max clock Twowire serial control interface Onchip PLL, . to MHz clock input Analog power supp ...

Reference Manual

... Although the FPGA, memory IC, and the board itself are capable of the maximum data rate of 667Mbps, the limitations in the clock generation primitives restrict the clock frequencies that can be generated from the 100 MHz system clock. Thus, for simplicity, the next highest data rate of 650Mbps is re ...

... Although the FPGA, memory IC, and the board itself are capable of the maximum data rate of 667Mbps, the limitations in the clock generation primitives restrict the clock frequencies that can be generated from the 100 MHz system clock. Thus, for simplicity, the next highest data rate of 650Mbps is re ...

PIN ASSIGNMENT FEATURES

... The next 4 bytes of the EPROM Status Memory contain the Page Address Redirection Bytes, which indicate if one or more of the pages of data in the 1024-bit EPROM section have been invalidated and redirected to the page address contained in the appropriate redirection byte. The hardware of the DS2502 ...

... The next 4 bytes of the EPROM Status Memory contain the Page Address Redirection Bytes, which indicate if one or more of the pages of data in the 1024-bit EPROM section have been invalidated and redirected to the page address contained in the appropriate redirection byte. The hardware of the DS2502 ...

docx

... 2) To facilitate portability between operating systems, file names used in the EMD file must only have lower case characters. File names should have a base name of no more than forty (40) characters followed by a period (“.”), followed by a file name extension of no more than three characters. The f ...

... 2) To facilitate portability between operating systems, file names used in the EMD file must only have lower case characters. File names should have a base name of no more than forty (40) characters followed by a period (“.”), followed by a file name extension of no more than three characters. The f ...

DDR2-533 Memory Design Guide for Two-DIMM

... On a DDR2 memory bus, the address and command signals are unidirectional signals that are always driven by the memory controller. For DDR2-533, the address runs at a clock rate of 266 MHz. The address and command signals are captured at the DRAM using the memory clocks. For a system with two unbuffe ...

... On a DDR2 memory bus, the address and command signals are unidirectional signals that are always driven by the memory controller. For DDR2-533, the address runs at a clock rate of 266 MHz. The address and command signals are captured at the DRAM using the memory clocks. For a system with two unbuffe ...

Advanced xDSL Line Testing and Fault Location for

... and evaluating the signal received based on knowledge of the signal transmitted from the source. The CPE sends the measurements to the DSLAM via a management channel, and the DSLAM then makes available both the downstream and the upstream measurement data through the management interface. DELT measu ...

... and evaluating the signal received based on knowledge of the signal transmitted from the source. The CPE sends the measurements to the DSLAM via a management channel, and the DSLAM then makes available both the downstream and the upstream measurement data through the management interface. DELT measu ...

5176 Predko Chapter 06

... in input mode and the Data Out pin will drive its value to not only the PICmicro® MCU’s I/O pin, but the Data In pin as well. In this situation, the Data In pin should not be latching any Data In. To avoid this, in most cases where this circuit combines input and output, the two input and output pin ...

... in input mode and the Data Out pin will drive its value to not only the PICmicro® MCU’s I/O pin, but the Data In pin as well. In this situation, the Data In pin should not be latching any Data In. To avoid this, in most cases where this circuit combines input and output, the two input and output pin ...

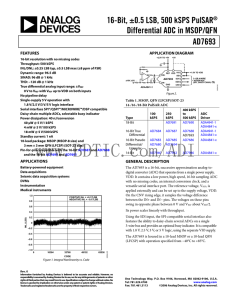

AD7693 数据手册DataSheet下载

... Serial Data Output. The conversion result is output on this pin. It is synchronized to SCK. Serial Data Clock Input. When the part is selected, the conversion result is shifted out by this clock. Serial Data Input. This input provides multiple features. It selects the interface mode of the ADC as fo ...

... Serial Data Output. The conversion result is output on this pin. It is synchronized to SCK. Serial Data Clock Input. When the part is selected, the conversion result is shifted out by this clock. Serial Data Input. This input provides multiple features. It selects the interface mode of the ADC as fo ...

Principles of Electronic Communication Systems

... Transmission Media and Bandwidth Twisted-pair is available as unshielded (UTP) or ...

... Transmission Media and Bandwidth Twisted-pair is available as unshielded (UTP) or ...

USER MANUAL REVISION PORTS ETC DCB-264 USERS GUIDE

... The physical direction of the motor with respect to the direction input will depend on the connection of the motor windings. To reverse the direction of the motor with respect to the direction input, switch the wires on phase 1 or phase 2 of the outputs. ...

... The physical direction of the motor with respect to the direction input will depend on the connection of the motor windings. To reverse the direction of the motor with respect to the direction input, switch the wires on phase 1 or phase 2 of the outputs. ...

Understanding Metastability in FPGAs

... If a data signal transition violates a register’s tSU or tH requirements, the output of the register may go into a metastable state. In a metastable state, the register output hovers at a value between the high and low states for some period of time, which means the output transition to a defined hi ...

... If a data signal transition violates a register’s tSU or tH requirements, the output of the register may go into a metastable state. In a metastable state, the register output hovers at a value between the high and low states for some period of time, which means the output transition to a defined hi ...

MAX5418LETA-T Datasheet

... 0.5V). See Supply Current vs. Digital Input Voltage in the Typical Operating Characteristics. Note 5: Wiper at midscale with a 10pF load (DC measurement). L = GND; an AC source is applied to H; and the W output is measured. A 3dB bandwidth occurs when the AC W/H value is 3dB lower than the DC W/H va ...

... 0.5V). See Supply Current vs. Digital Input Voltage in the Typical Operating Characteristics. Note 5: Wiper at midscale with a 10pF load (DC measurement). L = GND; an AC source is applied to H; and the W output is measured. A 3dB bandwidth occurs when the AC W/H value is 3dB lower than the DC W/H va ...

Testing2

... device can be triggered externally but the internal trigger works fine as well for frequencies up to 1 MHz. Each channel's output can be delayed in reference to any other channel or the trigger. This comes in handy when measuring jitter and width. One channel's output can be sent to the scope to act ...

... device can be triggered externally but the internal trigger works fine as well for frequencies up to 1 MHz. Each channel's output can be delayed in reference to any other channel or the trigger. This comes in handy when measuring jitter and width. One channel's output can be sent to the scope to act ...

DesignCon 2008 Solutions for Causal Modeling and A Technique

... It is well-understood by today’s signal integrity (SI) engineers that efficient design and verification of high-speed component electrical performance is best done through accurate modeling. When working in the multi-GHz frequency range, this modeling typically requires full-wave electromagnetic ana ...

... It is well-understood by today’s signal integrity (SI) engineers that efficient design and verification of high-speed component electrical performance is best done through accurate modeling. When working in the multi-GHz frequency range, this modeling typically requires full-wave electromagnetic ana ...

Input Impedance Measurement Using ADC FFT

... analog network response before RSx if the change in RSx value does not affect the analog network response. In other words, if RSx does not change the signal behavior at the earlier stages, then the measurement result is a function of RSx and the ADC input impedance only. ...

... analog network response before RSx if the change in RSx value does not affect the analog network response. In other words, if RSx does not change the signal behavior at the earlier stages, then the measurement result is a function of RSx and the ADC input impedance only. ...

Built-In System Protection for Industrial Drives

... in various configurations. The F2837xD contains three X-BARs: the Input X-BAR, the Output X-BAR, and the ePWM X-BAR. The Input X-BAR is used to route external GPIO signals into the device. It has access to every GPIO pin, where each signal can be routed to any or multiple destinations which include ...

... in various configurations. The F2837xD contains three X-BARs: the Input X-BAR, the Output X-BAR, and the ePWM X-BAR. The Input X-BAR is used to route external GPIO signals into the device. It has access to every GPIO pin, where each signal can be routed to any or multiple destinations which include ...

DW1000 Datasheet

... The DW1000, as supplied from Decawave, has not been certified for use in any particular geographic region by the appropriate regulatory body governing radio emissions in that region although it is capable of such certification depending on the region and the manner in which it is used. All products ...

... The DW1000, as supplied from Decawave, has not been certified for use in any particular geographic region by the appropriate regulatory body governing radio emissions in that region although it is capable of such certification depending on the region and the manner in which it is used. All products ...

Lumi_Days_V3-1

... Two methods of readout All four quadrants read out for each bunch and turn Data is processed in two ways Counting Mode (currently recorded for left side of each IP) Each bunch is counted as a “1” if exceeds a certain threshold Software integrates over a specific number of turns At lower luminosity ...

... Two methods of readout All four quadrants read out for each bunch and turn Data is processed in two ways Counting Mode (currently recorded for left side of each IP) Each bunch is counted as a “1” if exceeds a certain threshold Software integrates over a specific number of turns At lower luminosity ...

Atmel AT42QT1011 Single-key QTouch Touch Sensor IC Features

... SYNC Mode It is possible to synchronize the device to an external clock source by placing an appropriate waveform on the SYNC pin. SYNC mode can synchronize multiple QT1011 devices to each other to prevent cross-interference, or it can be used to enhance noise immunity from low frequency sources suc ...

... SYNC Mode It is possible to synchronize the device to an external clock source by placing an appropriate waveform on the SYNC pin. SYNC mode can synchronize multiple QT1011 devices to each other to prevent cross-interference, or it can be used to enhance noise immunity from low frequency sources suc ...

DR240 Hybrid Recorder

... instruments in the DARWIN series. Like the standard DAQ32, this software includes hardware setup, simplified data logging, simplified data viewing, data conversion (Excel, Lotus 1-2-3 or ASCII format), preference setting, system diagnosis, calibration, and tag number setting functions, all in one pa ...

... instruments in the DARWIN series. Like the standard DAQ32, this software includes hardware setup, simplified data logging, simplified data viewing, data conversion (Excel, Lotus 1-2-3 or ASCII format), preference setting, system diagnosis, calibration, and tag number setting functions, all in one pa ...

TZA1038HW

... RF outputs RFP and RFN can be DC coupled to the Analog-to-Digital Converter (ADC) of the decoder. The RF input signals are from photodiodes and have a large DC content by nature. This DC component must be removed from the signals for good system performance. Built-in DACs, located after the input st ...

... RF outputs RFP and RFN can be DC coupled to the Analog-to-Digital Converter (ADC) of the decoder. The RF input signals are from photodiodes and have a large DC content by nature. This DC component must be removed from the signals for good system performance. Built-in DACs, located after the input st ...

TR41.9.2-03-11-036-BillingProtection

... The contributor grants a free, irrevocable license to the Telecommunications Industry Association (TIA) to incorporate text or other copyrightable material contained in this contribution and any modifications thereof in the creation of a TIA Publication; to copyright and sell in TIA's name any TIA P ...

... The contributor grants a free, irrevocable license to the Telecommunications Industry Association (TIA) to incorporate text or other copyrightable material contained in this contribution and any modifications thereof in the creation of a TIA Publication; to copyright and sell in TIA's name any TIA P ...

MAX3892 +3.3V, 2.5Gbps/2.7Gbps, SDH/SONET 4:1 Serializer with Clock Synthesis General Description

... In 622MHz clock mode, the parallel data is clocked in by the rising edge of the 622MHz/666MHz parallel clock input. In the 311MHz clock mode, the parallel data is clocked in on both the rising and falling edges of the clock. The parallel input setup and hold time increases by 60ps if the duty cycle ...

... In 622MHz clock mode, the parallel data is clocked in by the rising edge of the 622MHz/666MHz parallel clock input. In the 311MHz clock mode, the parallel data is clocked in on both the rising and falling edges of the clock. The parallel input setup and hold time increases by 60ps if the duty cycle ...