Modified SET D-Flip Flop Design for Low

... SET D flip-flop [11] is shown in figure 2. In this design the feedback circuit of the master section is removed and in slave section, feedback loop consists of transmission gate. When clock level is ‘HIGH’, master latch is functional and the inverse of the data is stored to an intermediate node X. W ...

... SET D flip-flop [11] is shown in figure 2. In this design the feedback circuit of the master section is removed and in slave section, feedback loop consists of transmission gate. When clock level is ‘HIGH’, master latch is functional and the inverse of the data is stored to an intermediate node X. W ...

555 TIMER

... Known as shoot multivibrator Pulse generator circuit which the period is calculated from RC network and connected to external of 555 timer Stable when the output logic LOW (logic = 0) When a pulse is trigger at pin 2 (normally negative trigger pulse), timer output will change to HIGH (+Vs) for a whi ...

... Known as shoot multivibrator Pulse generator circuit which the period is calculated from RC network and connected to external of 555 timer Stable when the output logic LOW (logic = 0) When a pulse is trigger at pin 2 (normally negative trigger pulse), timer output will change to HIGH (+Vs) for a whi ...

DN520 - Versatile Industrial Power Supply Takes High Voltage Input

... Unique Power Control and Features The I2C interface allows extensive control of regulator operation. Each regulator may be set to a high efficiency Burst Mode® operation to save power at light loads or set to forced continuous mode for lower output ripple voltage. Each regulator can also have the s ...

... Unique Power Control and Features The I2C interface allows extensive control of regulator operation. Each regulator may be set to a high efficiency Burst Mode® operation to save power at light loads or set to forced continuous mode for lower output ripple voltage. Each regulator can also have the s ...

FIN1031 3.3V LVDS 4-Bit High Speed Differential Driver FI N1031

... This quad driver is designed for high speed interconnects utilizing Low Voltage Differential Signaling (LVDS) technology. The driver translates LVTTL signal levels to LVDS levels with a typical differential output swing of 350mV which provides low EMI at ultra low power dissipation even at high freq ...

... This quad driver is designed for high speed interconnects utilizing Low Voltage Differential Signaling (LVDS) technology. The driver translates LVTTL signal levels to LVDS levels with a typical differential output swing of 350mV which provides low EMI at ultra low power dissipation even at high freq ...

74LCX162374 Low Voltage 16-Bit D-Type Flip-Flop with 5V Tolerant Inputs and Outputs

... The LCX162374 consists of sixteen edge-triggered flip-flops with individual D-type inputs and 3-STATE true outputs. The device is byte controlled with each byte functioning identically, but independent of the other. The control pins can be shorted together to obtain full 16-bit operation. Each byte ...

... The LCX162374 consists of sixteen edge-triggered flip-flops with individual D-type inputs and 3-STATE true outputs. The device is byte controlled with each byte functioning identically, but independent of the other. The control pins can be shorted together to obtain full 16-bit operation. Each byte ...

MAX9600-02 - Part Number Search

... The MAX9600/MAX9601/MAX9602 ultra-high-speed comparators feature extremely low propagation delay (500ps). These dual and quad comparators minimize propagation delay skew (10ps) and are designed for low propagation delay dispersion (30ps). These features make them ideal for applications where high-fi ...

... The MAX9600/MAX9601/MAX9602 ultra-high-speed comparators feature extremely low propagation delay (500ps). These dual and quad comparators minimize propagation delay skew (10ps) and are designed for low propagation delay dispersion (30ps). These features make them ideal for applications where high-fi ...

Inverting Amplifier

... • Although you would zero voltage, there is actually an error voltage present at its output. • What causes this error? You can trace the error back to a number of unbalances in the op amp's internal transistors and resistors. To account for this in a circuit design, the net error is modeled as an of ...

... • Although you would zero voltage, there is actually an error voltage present at its output. • What causes this error? You can trace the error back to a number of unbalances in the op amp's internal transistors and resistors. To account for this in a circuit design, the net error is modeled as an of ...

Comparators

... Many comparators have an internal latch. The latch-enable signal has two states: compare (track) and latch (hold). When the latch-enable signal is in the compare state, the comparator output continuously responds to the sign of the net differential input signal. When the latch-enable signal transiti ...

... Many comparators have an internal latch. The latch-enable signal has two states: compare (track) and latch (hold). When the latch-enable signal is in the compare state, the comparator output continuously responds to the sign of the net differential input signal. When the latch-enable signal transiti ...

Low Power Pulse Width Modulator

... providing pulse-by-pulse overcurrent control for excessive loads. This comparator also causes CF to be charged for the remainder of the clock cycle. The charging current is ...

... providing pulse-by-pulse overcurrent control for excessive loads. This comparator also causes CF to be charged for the remainder of the clock cycle. The charging current is ...

DS1307 64 x 8 Serial Real

... Bus not busy: Both data and clock lines remain HIGH. Start data transfer: A change in the state of the data line, from HIGH to LOW, while the clock is HIGH, defines a START condition. Stop data transfer: A change in the state of the data line, from LOW to HIGH, while the clock line is HIGH, defines ...

... Bus not busy: Both data and clock lines remain HIGH. Start data transfer: A change in the state of the data line, from HIGH to LOW, while the clock is HIGH, defines a START condition. Stop data transfer: A change in the state of the data line, from LOW to HIGH, while the clock line is HIGH, defines ...

LMH2191 Dual Channel 52 MHz Clock Tree Driver (Rev. D)

... The clock tree driver consists of one input that drives 2 outputs. It is supplied by a high-precision voltage regulator of 1.8V, the LDO. The Clock outputs are enabled when the appropriate Clock Request inputs are logic high. Clock Tree Driver Input The source clock input (SCLK_IN) is the input for ...

... The clock tree driver consists of one input that drives 2 outputs. It is supplied by a high-precision voltage regulator of 1.8V, the LDO. The Clock outputs are enabled when the appropriate Clock Request inputs are logic high. Clock Tree Driver Input The source clock input (SCLK_IN) is the input for ...

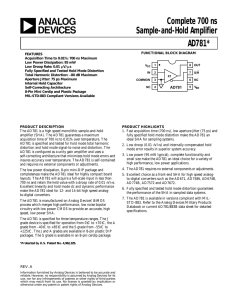

a Complete 700 ns Sample-and-Hold Amplifier AD781*

... small size make the AD781 an ideal choice for a variety of high performance, low power applications. 5. Excellent choice as a front-end SHA for high speed analogto-digital converters such as the AD671, AD7586, AD674B, AD774B, AD7572 and AD7672. 6. Fully specified and tested hold mode distortion guar ...

... small size make the AD781 an ideal choice for a variety of high performance, low power applications. 5. Excellent choice as a front-end SHA for high speed analogto-digital converters such as the AD671, AD7586, AD674B, AD774B, AD7572 and AD7672. 6. Fully specified and tested hold mode distortion guar ...

Lecture 37: CMOS Digital Logic Inverter.

... 2. The static power dissipation is nearly zero (a fraction of a W) in both states. The dynamic power dissipation is not zero as the gates are changing states. 3. Low output resistance in either state: low resistance to ground in the “low” output state, and low resistance to VDD in the “high” state. ...

... 2. The static power dissipation is nearly zero (a fraction of a W) in both states. The dynamic power dissipation is not zero as the gates are changing states. 3. Low output resistance in either state: low resistance to ground in the “low” output state, and low resistance to VDD in the “high” state. ...

Systems Concepts - Keith E. Holbert

... • In broad terms, a system that does not change with time is a time-invariant system; that is, the rule used to compute the system output does not depend on the time at which the input is applied • The coefficients to any algebraic or differential equations must be constant for the system to be time ...

... • In broad terms, a system that does not change with time is a time-invariant system; that is, the rule used to compute the system output does not depend on the time at which the input is applied • The coefficients to any algebraic or differential equations must be constant for the system to be time ...

DS90CP22.pdf

... required. When the driver is off, the link is in-active. If failsafe biasing is required, this can be accomplished with external high value resistors. The IN+ should be pull to Vcc with 10kΩ and the IN− should be pull to Gnd with 10kΩ. This provides a slight positive differential bias, and sets a kn ...

... required. When the driver is off, the link is in-active. If failsafe biasing is required, this can be accomplished with external high value resistors. The IN+ should be pull to Vcc with 10kΩ and the IN− should be pull to Gnd with 10kΩ. This provides a slight positive differential bias, and sets a kn ...

Action PAK ®

... AP7500’s 6V square wave output can be used to drive electronic counters (DTL, TTL, CMOS). The AP7501 can be used to drive electromechanical counters when connected to an external AC or DC power source. In the AP7501, the DPDT relay contacts are pulsed (closed) for only a short duration (100 millisec ...

... AP7500’s 6V square wave output can be used to drive electronic counters (DTL, TTL, CMOS). The AP7501 can be used to drive electromechanical counters when connected to an external AC or DC power source. In the AP7501, the DPDT relay contacts are pulsed (closed) for only a short duration (100 millisec ...

ES2898/ES2828 V.90/V.92 PCI DSP Modem Solution Product Brief

... General-purpose programmable bidirectional flag. These pins can be used for interfacing with a telephone or other device, performing such functions as phone-off-hook, phone-on-hook, ring, caller ID, etc. PF[0] is specially designed to support the ring function. ...

... General-purpose programmable bidirectional flag. These pins can be used for interfacing with a telephone or other device, performing such functions as phone-off-hook, phone-on-hook, ring, caller ID, etc. PF[0] is specially designed to support the ring function. ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.