Evaluate: MAX19505–MAX19507/MAX19515–MAX19517 MAX19505–MAX19507/ MAX19515–MAX19517 Evaluation Kits General Description

... kits are fully assembled and tested surface-mount boards. Follow the steps below to verify board operation. Caution: Do not turn on power supplies or enable signal generators until all connections are completed. 1) Verify that shunts are installed across pins 1-3 of jumpers JU1, JU2, and JU3 (SPI co ...

... kits are fully assembled and tested surface-mount boards. Follow the steps below to verify board operation. Caution: Do not turn on power supplies or enable signal generators until all connections are completed. 1) Verify that shunts are installed across pins 1-3 of jumpers JU1, JU2, and JU3 (SPI co ...

Considerations for Analog Input and Output

... The analog interface devices we use will typically have two to four grounds specified. They can include analog input ground (AI GND), analog output ground (AO GND), digital ground (D GND), and chassis ground (CHS GND). These grounds are not guaranteed to be equal in voltage. The first three are actu ...

... The analog interface devices we use will typically have two to four grounds specified. They can include analog input ground (AI GND), analog output ground (AO GND), digital ground (D GND), and chassis ground (CHS GND). These grounds are not guaranteed to be equal in voltage. The first three are actu ...

p9 - VADA

... Reorder the equivalent inputs to a transistor based on critical path delays and power consumption N- input Primitive CMOS logic – symmetrical in function level – antisymmetrical in Tr level • capacitance of output stage • body effect Scheme – The signal that has many transition must be far from outp ...

... Reorder the equivalent inputs to a transistor based on critical path delays and power consumption N- input Primitive CMOS logic – symmetrical in function level – antisymmetrical in Tr level • capacitance of output stage • body effect Scheme – The signal that has many transition must be far from outp ...

Encoder Signal Broadcaster

... for signal processing options, such as anti-dither filter, integer countdown or pulse and direction outputs, to be incorporated into each of the four broadcast signals independently. The broadcaster is ideal for driving multiple receivers from a single encoder in applications like electronic line sh ...

... for signal processing options, such as anti-dither filter, integer countdown or pulse and direction outputs, to be incorporated into each of the four broadcast signals independently. The broadcaster is ideal for driving multiple receivers from a single encoder in applications like electronic line sh ...

CERN/EP/ATE/DQ TTCvx _____________________________________________________________________________________

... Supply voltage regulators and backplane connections All ECL integrated circuits are referenced to the +5 V (VCC) rail (PECL). The PLL circuit has a maximum supply voltage of 3.3 V between VCC and GND, hence a 1.7 V current sinking regulator is implemented. Another voltage regulator is used to supply ...

... Supply voltage regulators and backplane connections All ECL integrated circuits are referenced to the +5 V (VCC) rail (PECL). The PLL circuit has a maximum supply voltage of 3.3 V between VCC and GND, hence a 1.7 V current sinking regulator is implemented. Another voltage regulator is used to supply ...

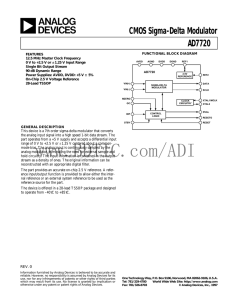

AD7720 数据手册DataSheet下载

... Analog Input Range Select, Logic Input. A logic low on this input selects unipolar mode. A logic high selects bipolar mode. MZERO Digital Control Input. When MZERO is high, the modulator inputs are internally grounded, i.e., tied to AGND in unipolar mode and REF2 in bipolar mode. MZERO allows on-chi ...

... Analog Input Range Select, Logic Input. A logic low on this input selects unipolar mode. A logic high selects bipolar mode. MZERO Digital Control Input. When MZERO is high, the modulator inputs are internally grounded, i.e., tied to AGND in unipolar mode and REF2 in bipolar mode. MZERO allows on-chi ...

AC Characteristics of MM74HC High-Speed CMOS

... Another speed consideration, though not directly related to propagation delays, is input rise and fall time. As with other high-speed logic families and also CD4000B and 74C CMOS, slow input rise and fall times on input signals can cause logic problems. Typically, small signal gains for a MM74HC gat ...

... Another speed consideration, though not directly related to propagation delays, is input rise and fall time. As with other high-speed logic families and also CD4000B and 74C CMOS, slow input rise and fall times on input signals can cause logic problems. Typically, small signal gains for a MM74HC gat ...

a 750 MHz, 3.8 mA 10 ns Switching Multiplexers AD8180/AD8182*

... Figure 17. Disabled Output and Input Impedance vs. Frequency ...

... Figure 17. Disabled Output and Input Impedance vs. Frequency ...

SN74HC74

... ‡ Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not implied. Exposure to ...

... ‡ Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not implied. Exposure to ...

AN3 - Applications for a Switched-Capacitor Instrumentation Building Block

... functions. Their operation is usually described in terms of voltage and current. Switched-capacitor based circuits are sampled data systems which approximate continuous functions with bandwidth limited by the sampling frequency. Their operation is described in the distribution of charge over time. T ...

... functions. Their operation is usually described in terms of voltage and current. Switched-capacitor based circuits are sampled data systems which approximate continuous functions with bandwidth limited by the sampling frequency. Their operation is described in the distribution of charge over time. T ...

AD633 Low Cost Analog Multiplier

... The AD633 is well suited for such applications as modulation and demodulation, automatic gain control, power measurement, voltage controlled amplifiers, and frequency doublers. Note that these applications show the pin connections for the AD633JN pinout (8-pin DIP), which differs from the AD633JR pi ...

... The AD633 is well suited for such applications as modulation and demodulation, automatic gain control, power measurement, voltage controlled amplifiers, and frequency doublers. Note that these applications show the pin connections for the AD633JN pinout (8-pin DIP), which differs from the AD633JR pi ...

The SiI 170B PanelLink Transmitter

... • Data Enable (DE) generated from HSYNC and VSYNC • Inter-pair skew tolerance up to 1 input clock cycle (6 ns at 165 MHz) • Adjustable TMDS low-voltage swing ...

... • Data Enable (DE) generated from HSYNC and VSYNC • Inter-pair skew tolerance up to 1 input clock cycle (6 ns at 165 MHz) • Adjustable TMDS low-voltage swing ...

AD7894 数据手册DataSheet下载

... provides the user with signal scaling, track/hold, A/D converter and serial interface logic functions on a single chip. The A/D converter section of the AD7894 consists of a conventional successive-approximation converter based around an R-2R ladder structure. The signal scaling on the AD7894-10 and ...

... provides the user with signal scaling, track/hold, A/D converter and serial interface logic functions on a single chip. The A/D converter section of the AD7894 consists of a conventional successive-approximation converter based around an R-2R ladder structure. The signal scaling on the AD7894-10 and ...

ADV7128 数据手册DataSheet 下载

... which is what most monitors are rated as. The analog output configurations to drive such loads are described in the Analog Interface section and illustrated in Figure 5. However, in some applications it may be required to drive long “transmission line” cable lengths. Cable lengths greater than 10 me ...

... which is what most monitors are rated as. The analog output configurations to drive such loads are described in the Analog Interface section and illustrated in Figure 5. However, in some applications it may be required to drive long “transmission line” cable lengths. Cable lengths greater than 10 me ...

ENGG2410 Digital Design

... Any digital circuit can be designed and realized using AND, OR, NOT gates If we can prove that NAND gate can emulate AND, OR, NOT, then we prove that it is Universal ...

... Any digital circuit can be designed and realized using AND, OR, NOT gates If we can prove that NAND gate can emulate AND, OR, NOT, then we prove that it is Universal ...

ULTRA SLIMPAK G168-0001 ® DC Powered AC Input Limit Alarm

... minimize all lead lengths. For AC inductive loads, place a properly rated MOV across the load in parallel with a series RC snubber. Use a 0.01 to 0.1uF pulse film capacitor (foil polypropylene recommended) of sufficient voltage, and a 47 ohm, 1/2W carbon resistor. For DC inductive loads, place a dio ...

... minimize all lead lengths. For AC inductive loads, place a properly rated MOV across the load in parallel with a series RC snubber. Use a 0.01 to 0.1uF pulse film capacitor (foil polypropylene recommended) of sufficient voltage, and a 47 ohm, 1/2W carbon resistor. For DC inductive loads, place a dio ...

Pendulum MDP-1 Operating Manual

... detail that meets the requirements of the most demanding recording applications. Our short signal path design excels in audio performance, delivering extremely wide bandwidth, low noise, and high headroom. The MDP-1 has all the things you'd expect in a full-featured mic preamp, including phantom pow ...

... detail that meets the requirements of the most demanding recording applications. Our short signal path design excels in audio performance, delivering extremely wide bandwidth, low noise, and high headroom. The MDP-1 has all the things you'd expect in a full-featured mic preamp, including phantom pow ...

MAX1426 10-Bit, 10Msps ADC General Description Features

... code. A DAC converts the ADC result back into an analog voltage, which is subtracted from the held input signal. The resulting error signal is then multiplied by two, and this product is passed along to the next pipeline stage where the process is repeated. Digital error correction compensates for o ...

... code. A DAC converts the ADC result back into an analog voltage, which is subtracted from the held input signal. The resulting error signal is then multiplied by two, and this product is passed along to the next pipeline stage where the process is repeated. Digital error correction compensates for o ...

MAX9160 LVDS or LVTTL/LVCMOS Input to 14 LVTTL/LVCMOS Output Clock Driver General Description

... Without a fail-safe circuit, when the LVDS input is selected and undriven, noise may cause the enabled outputs to switch. Open or undriven terminated input conditions can occur when a cable is disconnected or cut, or when a driver output is in high impedance. A shorted input can occur because of a c ...

... Without a fail-safe circuit, when the LVDS input is selected and undriven, noise may cause the enabled outputs to switch. Open or undriven terminated input conditions can occur when a cable is disconnected or cut, or when a driver output is in high impedance. A shorted input can occur because of a c ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.