Regulating Pulse Width Modulators

... The UC1525B/1527B series of pulse width modulator integrated circuits are designed to offer improved performance and lowered external parts count when used in designing all types of switching power supplies. The on-chip +5.1V buried zener reference is trimmed to ±0.75% and the input common-mode rang ...

... The UC1525B/1527B series of pulse width modulator integrated circuits are designed to offer improved performance and lowered external parts count when used in designing all types of switching power supplies. The on-chip +5.1V buried zener reference is trimmed to ±0.75% and the input common-mode rang ...

TL081 OpAmp - U.C.C. Physics Department

... will not change the phase of the output; however, if both inputs exceed the limit, the output of the amplifier will be forced to a high state. The amplifier will operate with a common-mode input voltage equal to the positive supply; however, the gain bandwidth and slew rate may be decreased in this ...

... will not change the phase of the output; however, if both inputs exceed the limit, the output of the amplifier will be forced to a high state. The amplifier will operate with a common-mode input voltage equal to the positive supply; however, the gain bandwidth and slew rate may be decreased in this ...

Understanding of IC555 Timer and IC 555 Timer Tester

... TR is falling edge sensitive instead of level sensitive). The NE555 parts were commercial temperature range, 0 °C to +70 °C, and the SE555 part number designated the military temperature range, −55 °C to +125 °C. These were available in both high-reliability metal can (T package) and inexpensive epo ...

... TR is falling edge sensitive instead of level sensitive). The NE555 parts were commercial temperature range, 0 °C to +70 °C, and the SE555 part number designated the military temperature range, −55 °C to +125 °C. These were available in both high-reliability metal can (T package) and inexpensive epo ...

X Features Description Models Input Specifications

... Surge Immunity Test: AC Power Line: line to line 4 kV, line to earth 6 kV ...

... Surge Immunity Test: AC Power Line: line to line 4 kV, line to earth 6 kV ...

Bellofram T1500 IP Transducer Installation Instructions

... 6). The zero adjustment causes the nozzle to move relative to the flexure. The span adjustment is a potentiometer that limits the flow of current through the coil. A thermistor circuit in series with the coil provides temperature compensation. ...

... 6). The zero adjustment causes the nozzle to move relative to the flexure. The span adjustment is a potentiometer that limits the flow of current through the coil. A thermistor circuit in series with the coil provides temperature compensation. ...

SPREAD SPECTRUM CLOCK SYNTHESIZER IDT5P50901/2/3/4

... the component side of the board as close to the VDD pin as possible. No vias should be used between the decoupling capacitors and VDD pins. The PCB trace to VDD pins should be kept as short as possible, as should the PCB trace to the ground via. ...

... the component side of the board as close to the VDD pin as possible. No vias should be used between the decoupling capacitors and VDD pins. The PCB trace to VDD pins should be kept as short as possible, as should the PCB trace to the ground via. ...

Features •

... • The DATA output of the AT17FxxA Series Configurator drives DIN of the FPGA devices. • The DCLK output of the AT17FxxA device drives the DCLK input data of the FPGA. • The nCASC output of a AT17FxxA Series Configurator drives the nCS input of the next Configurator in a cascade chain of configurator ...

... • The DATA output of the AT17FxxA Series Configurator drives DIN of the FPGA devices. • The DCLK output of the AT17FxxA device drives the DCLK input data of the FPGA. • The nCASC output of a AT17FxxA Series Configurator drives the nCS input of the next Configurator in a cascade chain of configurator ...

presentation

... High switching frequency saves area Combined drivers saves area and switching loss Recycled charge converter load discharges Cclk Unique ZVS delay circuit lower power loss ...

... High switching frequency saves area Combined drivers saves area and switching loss Recycled charge converter load discharges Cclk Unique ZVS delay circuit lower power loss ...

UcD32MP UcD34MP UcD36MP

... the overload condition remains for a longer time the supply will enter hiccup mode until the overload condition disappears. This feature combined with large electrolytic buffer capacitors leads to the capability of delivering high dynamic headroom power to the connected amplifier. The UcD3xMP also i ...

... the overload condition remains for a longer time the supply will enter hiccup mode until the overload condition disappears. This feature combined with large electrolytic buffer capacitors leads to the capability of delivering high dynamic headroom power to the connected amplifier. The UcD3xMP also i ...

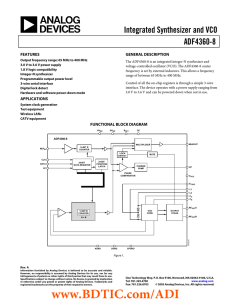

ADF4360-8 数据手册DataSheet 下载

... Reference Input. This is a CMOS input with a nominal threshold of VDD/2 and a dc equivalent input resistance of 100 kΩ (see Figure 16). This input can be driven from a TTL or CMOS crystal oscillator, or it can be ac-coupled. Serial Clock Input. This serial clock is used to clock in the serial data t ...

... Reference Input. This is a CMOS input with a nominal threshold of VDD/2 and a dc equivalent input resistance of 100 kΩ (see Figure 16). This input can be driven from a TTL or CMOS crystal oscillator, or it can be ac-coupled. Serial Clock Input. This serial clock is used to clock in the serial data t ...

MOS LSI

... Static logic is used to maximize flexibility of operation and to simplify the task of the user. The data holding registers are static and, will hold a data word until it is replaced by another word. Asynchronous operation allows the use of a single transmission line. The clock period has to be w ...

... Static logic is used to maximize flexibility of operation and to simplify the task of the user. The data holding registers are static and, will hold a data word until it is replaced by another word. Asynchronous operation allows the use of a single transmission line. The clock period has to be w ...

SYNCHRO RETRANSMISSION UNIT KW903-SP

... back-up means you can still use the autopilot. SYNCHRO OUTPUT. The “standard” and most common output is nominally 115v (50/60 Hz) reference, 90v line to line maximum voltage. Synchros are not critical on their voltage. The KW903 has several transformer taps to allow selecting reduced voltage, and by ...

... back-up means you can still use the autopilot. SYNCHRO OUTPUT. The “standard” and most common output is nominally 115v (50/60 Hz) reference, 90v line to line maximum voltage. Synchros are not critical on their voltage. The KW903 has several transformer taps to allow selecting reduced voltage, and by ...

FUNCTION manual

... Same as Voltage Controlled Triangle Function, only the output is taken from EOC or EOR. Using EOR, the RISE parameter will more effectively adjust frequency, and FALL parameter will adjust pulse width. Using EOC, the opposite is true: where Rise more effectively adjusts Width and Fall adjust frequen ...

... Same as Voltage Controlled Triangle Function, only the output is taken from EOC or EOR. Using EOR, the RISE parameter will more effectively adjust frequency, and FALL parameter will adjust pulse width. Using EOC, the opposite is true: where Rise more effectively adjusts Width and Fall adjust frequen ...

16826 - Public Address System

... amplifier outputs 0.8 V to 10 000 Ohm or +10 dbm to 600 Ohm single ended. ...

... amplifier outputs 0.8 V to 10 000 Ohm or +10 dbm to 600 Ohm single ended. ...

MAX3311/MAX3313 460kbps, 1µA Supply Current, RS-232-Compatible Transceivers in µMAX General Description

... into three state. The transmitter input does not have an internal pullup resistor. ...

... into three state. The transmitter input does not have an internal pullup resistor. ...

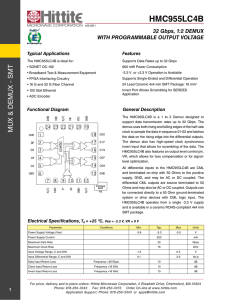

HMC955LC4B - Hittite Microwave Corporation

... support data transmission rates up to 32 Gbps. The demux uses both rising and falling edges of the half-rate clock to sample the data in sequence 01-02 and latches the data on the rising edge into the differential outputs. The demux also has high-speed clock synchronous invert input that allows for ...

... support data transmission rates up to 32 Gbps. The demux uses both rising and falling edges of the half-rate clock to sample the data in sequence 01-02 and latches the data on the rising edge into the differential outputs. The demux also has high-speed clock synchronous invert input that allows for ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.