PTN3381D - NXP Semiconductors

... (consisting of a clock and a data line) between 3.3 V source-side and 5 V sink-side. The DDC channel is implemented using active I2C-bus buffer technology providing capacitive isolation, redriving and level shifting as well as disablement (isolation between source and sink) of the clock and data lin ...

... (consisting of a clock and a data line) between 3.3 V source-side and 5 V sink-side. The DDC channel is implemented using active I2C-bus buffer technology providing capacitive isolation, redriving and level shifting as well as disablement (isolation between source and sink) of the clock and data lin ...

NTSX2102 1. General description Dual supply translating transceiver; open drain; auto

... The NTSX2102 can be used in point-to-point applications to interface between devices or systems operating at different supply voltages. The device is targeted at I2C or 1-wire buses which use open-drain drivers. ...

... The NTSX2102 can be used in point-to-point applications to interface between devices or systems operating at different supply voltages. The device is targeted at I2C or 1-wire buses which use open-drain drivers. ...

IN-1 : 2013 GATE Questions

... In the circuit shown below, Q1 has negligible collector – to – emitter saturation voltage and the diode drops negligible voltage across it under forward bias. If Vcc is +5 V, X and Y are digital signals with 0 V as logic 0 and as logic 1, then the Boolean expression for Z is R1 ...

... In the circuit shown below, Q1 has negligible collector – to – emitter saturation voltage and the diode drops negligible voltage across it under forward bias. If Vcc is +5 V, X and Y are digital signals with 0 V as logic 0 and as logic 1, then the Boolean expression for Z is R1 ...

An integrated CMOS optical receiver with clock and data recovery circuit

... higher speed operations, the open loop gain is necessarily reduced and the number of amplifying stages is decreased to minimise the excessive phase shift. As a result, a significant amount of noise is produced by the feedback resistor. Thus, tradeoffs between speed, transimpedance gain and sensitivi ...

... higher speed operations, the open loop gain is necessarily reduced and the number of amplifying stages is decreased to minimise the excessive phase shift. As a result, a significant amount of noise is produced by the feedback resistor. Thus, tradeoffs between speed, transimpedance gain and sensitivi ...

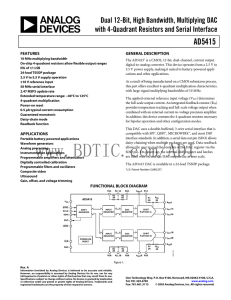

AD5415 数据手册DataSheet 下载

... VDD = 4.5 V to 5.5 V, ISOURCE = 200 μA VDD = 2.5 V to 3.6 V, ISOURCE = 200 μA VDD = 4.5 V to 5.5 V, ISINK = 200 μA VDD = 2.5 V to 3.6 V, ISINK = 200 μA ...

... VDD = 4.5 V to 5.5 V, ISOURCE = 200 μA VDD = 2.5 V to 3.6 V, ISOURCE = 200 μA VDD = 4.5 V to 5.5 V, ISINK = 200 μA VDD = 2.5 V to 3.6 V, ISINK = 200 μA ...

BQ24105-Q1 数据资料 dataSheet 下载

... Power-good status output (open drain). The transistor turns on when a valid VCC is detected. It is turned off in the sleep mode. PG can be used to drive a LED or communicate with a host processor. ...

... Power-good status output (open drain). The transistor turns on when a valid VCC is detected. It is turned off in the sleep mode. PG can be used to drive a LED or communicate with a host processor. ...

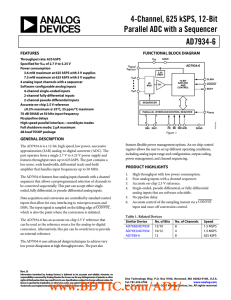

4-Channel, 625 kSPS, 12-Bit Parallel ADC with a Sequencer AD7934-6

... enabled. Data and the channel ID are transferred on Pin DB0 to Pin DB7, and Pin DB8/HBEN assumes its HBEN functionality. When operating in byte transfer mode, unused data lines should be tied off to DGND. Data Bit 0 to Data Bit 7. Three-state parallel digital I/O pins that provide the conversion res ...

... enabled. Data and the channel ID are transferred on Pin DB0 to Pin DB7, and Pin DB8/HBEN assumes its HBEN functionality. When operating in byte transfer mode, unused data lines should be tied off to DGND. Data Bit 0 to Data Bit 7. Three-state parallel digital I/O pins that provide the conversion res ...

Integrated Circuit Design of Sigma-Delta Modulator for

... The design of a sigma-delta modulator as part of an analog-to-digital converter for a monolithic electric energy measurement system is presented. The main requirements such applications are a resolution of 16 bits and a bandwidth ranging from 40 Hz to 2 KHz. The design was optimized at system level ...

... The design of a sigma-delta modulator as part of an analog-to-digital converter for a monolithic electric energy measurement system is presented. The main requirements such applications are a resolution of 16 bits and a bandwidth ranging from 40 Hz to 2 KHz. The design was optimized at system level ...

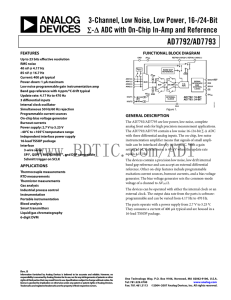

AD7792 数据手册DataSheet下载

... generator. The bias voltage generator sets the common-mode voltage of a channel to AVDD/2. The devices can be operated with either the internal clock or an external clock. The output data rate from the parts is softwareprogrammable and can be varied from 4.17 Hz to 470 Hz. The parts operate with a p ...

... generator. The bias voltage generator sets the common-mode voltage of a channel to AVDD/2. The devices can be operated with either the internal clock or an external clock. The output data rate from the parts is softwareprogrammable and can be varied from 4.17 Hz to 470 Hz. The parts operate with a p ...

AD7798 数据手册DataSheet下载

... Serial Clock Input. This serial clock input is for data transfers to and from the ADC. The SCLK has a Schmitt-triggered input, making the interface suitable for opto-isolated applications. The serial clock can be continuous, with all data transmitted in a continuous train of pulses. Alternatively, i ...

... Serial Clock Input. This serial clock input is for data transfers to and from the ADC. The SCLK has a Schmitt-triggered input, making the interface suitable for opto-isolated applications. The serial clock can be continuous, with all data transmitted in a continuous train of pulses. Alternatively, i ...

MAX8660/MAX8660A/MAX8660B/MAX8661 High-Efficiency, Low-I , PMICs with Dynamic Voltage Management for Mobile Applications

... Note 1: LX_ has internal clamp diodes to PG_ and PV_. Applications that forward bias these diodes must take care not to exceed the IC’s package power-dissipation limits. Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings o ...

... Note 1: LX_ has internal clamp diodes to PG_ and PV_. Applications that forward bias these diodes must take care not to exceed the IC’s package power-dissipation limits. Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings o ...

AN9405 - Intersil

... upper and lower MOSFETs differ, two sets of calculations must be done; one for the upper switches and one for the lower switches. The bias current budget for upper and lower switches will be the sum of each calculation. Always keep in mind that the lower bias supply must supply current to the upper ...

... upper and lower MOSFETs differ, two sets of calculations must be done; one for the upper switches and one for the lower switches. The bias current budget for upper and lower switches will be the sum of each calculation. Always keep in mind that the lower bias supply must supply current to the upper ...

DS4426 Quad-Channel, I C-Margining IDACs with Three Channels of Power-Supply Tracking

... sourced when the power-supply tracking circuit is enabled. When the difference between the voltage presented to INP (V INP ) and INN (V INN ) is more than approximately +0.3V, then the maximum source current, as determined by the value IMAX, is sourced into the OUT pin connection. When the differenc ...

... sourced when the power-supply tracking circuit is enabled. When the difference between the voltage presented to INP (V INP ) and INN (V INN ) is more than approximately +0.3V, then the maximum source current, as determined by the value IMAX, is sourced into the OUT pin connection. When the differenc ...

LOC10c DC Circuits Resistors in Series and Parallel

... series and/or parallel. To understand this we need to understand some properties of potential difference and current better. First if there is only one path for the current to follow such as the series circuit shown in Figure 3, then the current has to have the same value everywhere in the circuit. ...

... series and/or parallel. To understand this we need to understand some properties of potential difference and current better. First if there is only one path for the current to follow such as the series circuit shown in Figure 3, then the current has to have the same value everywhere in the circuit. ...

Transistor–transistor logic

Transistor–transistor logic (TTL) is a class of digital circuits built from bipolar junction transistors (BJT) and resistors. It is called transistor–transistor logic because both the logic gating function (e.g., AND) and the amplifying function are performed by transistors (contrast with RTL and DTL).TTL is notable for being a widespread integrated circuit (IC) family used in many applications such as computers, industrial controls, test equipment and instrumentation, consumer electronics, synthesizers, etc. The designation TTL is sometimes used to mean TTL-compatible logic levels, even when not associated directly with TTL integrated circuits, for example as a label on the inputs and outputs of electronic instruments.After their introduction in integrated circuit form in 1963 by Sylvania, TTL integrated circuits were manufactured by several semiconductor companies, with the 7400 series (also called 74xx) by Texas Instruments becoming particularly popular. TTL manufacturers offered a wide range of logic gate, flip-flops, counters, and other circuits. Several variations from the original bipolar TTL concept were developed, giving circuits with higher speed or lower power dissipation to allow optimization of a design. TTL circuits simplified design of systems compared to earlier logic families, offering superior speed to resistor–transistor logic (RTL) and easier design layout than emitter-coupled logic (ECL). The design of the input and outputs of TTL gates allowed many elements to be interconnected.TTL became the foundation of computers and other digital electronics. Even after much larger scale integrated circuits made multiple-circuit-board processors obsolete, TTL devices still found extensive use as the ""glue"" logic interfacing more densely integrated components. TTL devices were originally made in ceramic and plastic dual-in-line (DIP) packages, and flat-pack form. TTL chips are now also made in surface-mount packages. Successors to the original bipolar TTL logic often are interchangeable in function with the original circuits, but with improved speed or lower power dissipation.