* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download A PASSIVE DAMPING NETWORK FOR SINGLE PHASE MATRIX

Spark-gap transmitter wikipedia , lookup

Ringing artifacts wikipedia , lookup

Mercury-arc valve wikipedia , lookup

Immunity-aware programming wikipedia , lookup

Mechanical filter wikipedia , lookup

Power engineering wikipedia , lookup

History of electric power transmission wikipedia , lookup

Three-phase electric power wikipedia , lookup

Electrical substation wikipedia , lookup

Electrical ballast wikipedia , lookup

Stray voltage wikipedia , lookup

Integrating ADC wikipedia , lookup

Power inverter wikipedia , lookup

Zobel network wikipedia , lookup

Power MOSFET wikipedia , lookup

Pulse-width modulation wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Variable-frequency drive wikipedia , lookup

Voltage optimisation wikipedia , lookup

Schmitt trigger wikipedia , lookup

Current source wikipedia , lookup

Voltage regulator wikipedia , lookup

Alternating current wikipedia , lookup

Distribution management system wikipedia , lookup

Two-port network wikipedia , lookup

Mains electricity wikipedia , lookup

Network analysis (electrical circuits) wikipedia , lookup

Current mirror wikipedia , lookup

Opto-isolator wikipedia , lookup

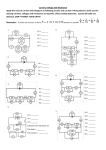

A PASSIVE DAMPING NETWORK FOR SINGLE PHASE MATRIX CONVERTER OPERATING AS A RECTIFIER PUTERI NOR ASHIKIN BINTI MEGAT YUNUS A project report submitted in partial fulfilment of the requirements for the award of degree of Master of Engineering (Electrical – Power) Faculty of Electrical Engineering Universiti Teknologi Malaysia NOVEMBER 2009 iii This is special dedicated to my beloved mother Suibah binti Alang Kassim , my father Megat Yunus bin Megat Ibrahim and my family for their continuous love and prayers , also to all my friends for their patient , kindness and cooperation . I wish to thanks all of you for your support during my studies in UTM. May God bless all of them. iv ACKNOWLEDGEMENT In the name of Allah S.W.T., the Most Beneficent, the Most Merciful. Foremost, all praise to Allah for the entire incredible gift endowed upon me and for giving me the health and strength to complete this final project. With this opportunity, I would like to express a special gratitude to my project supervisor Dr. Awang Bin Jusoh for his guidance, advice and willing in sharing the knowledge towards the completion of this final project. My deepest appreciation also goes to my beloved parent, Suibah binti Alang Kassim and En Megat Yunus bin Megat Ibrahim also family members for their faith and prayers that has enable for me to succeed. Without them, I would never finishup this project. Last but not least, I would like to take this opportunity to express my gratitude to all whose have been supportive and giving me courage, comfort and advices during the course of this project. v ABSTRACT This report presents the study of a Single Phase Matrix Converter (SPMC) operated as an AC-DC controlled rectifier driving the linear and non-linear load (constant power load). SPMC used the multiple PWM technique as its basic switching operation for synthesizing the required output. Modeling and analysis of CPL and passive damping network were conducted in detailed before been implemented in the SPMC system. The usage of LC filter at the DC side of the rectifier to generate smooth DC output creates non sinusoidal input current input containing a lot of harmonics. Passive damping network at the DC side was introduced to compensate this problem, however the system performances becomes worse if non-linear load such as constant power load is connected. The combination of modified input LC filter at the input side with the passive damping network at the DC side seems produced very good results. SPMC works well with this arrangement. A complete set of simulation results using MATLAB/Simulink to validate the analysis and design approach of SPWM were given. vi ABSTRAK Laporan ini mengemukakan kajian mengenai Penukar Matrik Satu Fasa (SPMC) berfungsi sebagai penerus terkawal AU-AT dalam memacu beban linear dan beban tidak linear (CPL). Bagi operasi asas, teknik gandaan Permodulatan Denyut Lebar (PWM) telah digunakan sebagai teknik pengsuisan dalam mensintesiskan keluaran yang diperlukan. Permodelan dan analisis terhadap beban tidak linear (CPL) dan rangkaian redaman pasif telah dilakukan sebelum diimplementasikan ke dalam sistem SPMC. Penggunaan penapis LC pada bahagian AT penerus dalam menjana voltan keluaran AT yang lebih licin telah menghasilkan sumber arus yang tidak sinus serta mengandungi lambakan harmonik. Rangkaian redaman pasif pada bahagian AT telah digunakan untuk mengatasi masalah ini. Walaubagaimanapun, prestasi SPMC menjadi bertambah buruk apabila beban tidak linear disambungkan. Penggunaan gabungan penapis LC yang telah diubah suai pada bahagian kemasukan bersama rangkaian redaman pasif pada bahagian keluaran AT telah menghasilkan keputusan yang sangat baik. SPMC berjalan lancar bersama susunan ini. Keputusan simulasi yang lengkap menggunakan Matlab/Simulink telah dihasilkan bagi mengesahkan keberkesanan analisa dan reka bentuk SPMC. vii TABLE OF CONTENTS CHAPTER 1 2 3 TITLE PAGE DECLARATION ii DEDICATION iii ACKNOWLEDGEMENT iv ABSTRACT v ABSTRAK vi TABLE OF CONTENTS vii LIST OF TABLES x LIST OF FIGURES xi LIST OF ABBREVIATIONS xv INTRODUCTION 1.1 Introduction 1 1.2 Converter Classification 2 1.3 Objective 3 1.4 Scope 3 1.5 Thesis Organization 4 SINGLE PHASE MATRIX CONVERTER (SPMC) 2.1 Introduction 5 2.2 Bi-directional Switch 6 SWITCHING STRATEGIES OF SPMC 3.1 Introduction 8 3.2 Insulated Gate Bipolar Transistor (IGBT) 8 3.3 Switching State of SPMC 11 viii 4 PASSIVE DAMPING NETWORK 4.1 Linear Analysis Technique 14 4.2 Stability Analysis of Impedance Based Criterion 14 4.3 LC Filter Output Impedance, Zo 16 4.4 Output to input Voltage Transfer Function 20 4.5 L-C Filter with Passive Damping Network 21 4.6 Analysis of LC Filter with Passive Damping 22 Network 5 4.7 Design of the Passive Damping Resistor 24 4.8 Design Input LC Filter with Damping Resistor 27 CONSTANT POWER LOAD 5.1 Introduction 31 5.2 Negative Input Resistance Phenomenon 31 5.3 Equilibrium Point 33 5.4 Simulation Model of Constant Power Load, CPL 35 5.4.1 L-C Filter with Series Loss Resistor and 36 CPL 5.4.2 L-C Filter with Passive Damping and 40 CPL 6 SIMULATION RESULTS AND DISCUSSION 6.1 Introduction 42 6.2 MATLAB/Simulink 42 6.3 Modelling Design 43 6.4 Simulation Results 49 6.4.1 Resistive Load without Filter 49 6.4.2 Adding L-C1 Filter 52 6.4.3 L-C1 Filter with Passive Damping 54 Network (R1,C2) ix 6.4.4 L-C1 Filter and Passive Damping 58 Network ( R1,C2) Driving a CPL 6.4.5 Adding LC Input Filter with Damping 62 Resistor at AC Side of the SPMC 6.5 Discussion 7 REFERENCES 63 CONCLUSION AND FUTURE DEVELOPMENT 7.1 Conclusion 65 7.2 Future Development 65 x LIST OF TABLES TABLE NO. TITLE PAGE 3.1 Typical ratings of high-power devices 10 6.1 Comparisons of THD supply current and ripple output voltage with L-C1 Filter 54 Comparisons of THD supply current and ripple output voltage with L-C1 Filter and Passive Damping Network (R1,C2) 57 Comparison of THD supply current when driving CPL at different switching frequency 61 Comparison of THD supply current when driving CPL at different switching frequency after adding LC input filter with damping resistor at AC side 63 6.5 Effect of increasing value of switching frequency 64 6.6 Comparison of THD supply current with increasing the switching frequency 64 6.2 6.3 6.4 xi LIST OF FIGURES FIGURES NO. TITLE PAGE 2.1 SPMC Circuit 5 2.2 Bidirectional Switch (common emitter arrangement) 6 3.1 IGBT Equivalent Circuit 9 3.2 N-channel IGBT symbol 10 3.3 I-V characteristics 11 3.4 State 1 AC Input (positive cycle) 12 3.5 State 2 AC Input (negative cycle) 12 3.6 State 3 AC Input (positive cycle) 13 3.7 State 4 AC Input (negative cycle) 13 4.1 Impedance Based Stability Criterion Circuit 15 4.2 Simple L-C filter 16 4.3 Using Laplace Transform 17 4.4 Filter Output Impedance 18 4.5 L-C Filter with Series Resistor Rs 19 4.6 Output Impedance of L-C filter with four different Rs 19 4.7 Voltage transfer function 20 4.8 L-C filter with passive damping network 22 4.9 The root locus plot of varying R for different C2. 24 4.10 Voltage transfer function Vc/Vs of the L-C filter with passive damping where L = 90 µF and C1 = 500 µF 27 xii 4.11 Possible connection of the resistor 28 4.12 Resistor connected in parallel with capacitor and its output to input voltage transfer function 28 Resistor connected in series with capacitor and its output to input voltage transfer function 28 Resistor connected in parallel with inductor and its output to input voltage transfer function 29 Resistor connected in series with inductor and its output to input voltage transfer function 29 4.16 Voltage transfer function for each connection of resistor 30 5.1 Constant Power Load 32 5.2 Static input voltage-current characteristic 32 5.3 Model of source connected to CPL via L-C Filter. 33 5.4 Source line and CPL characteristic 34 5.5 A block diagram of CPL model 35 5.6 Simulink block diagram of simulation model. 36 5.7 Plot of simulated CPL input voltage, Vc and inductor current iL at Vs = 270V 37 Plot of simulated CPL input voltage, Vc and inductor current iL at Vs = 200V 38 5.9 Plot of simulated CPL input voltage, Vc 39 5.10 Plot of simulated inductor current, iL 39 5.11 Simulation circuit configuration 40 5.12 Plot of simulated capacitor voltage, Vc for different CPL power values 41 Plot of simulated inductor current, iL for different CPL power values 41 Plot of simulated capacitor voltage, Vc and inductor current, iL at 4 kW power value. 41 4.13 4.14 4.15 5.8 5.13 5.14 xiii 6.1 Overall SPMC circuit connected with LC filter and Passive Damping Network driving a resistive load 44 Overall SPMC circuit connected with LC filter and Passive Damping Network driving a CPL 44 Overall SPMC circuit connected with LC filter and Passive Damping Network driving a CPL adding with LC input filter and damping resistor 45 6.4 SPMC Subsystem 45 6.5 Bidirectional switch 46 6.6 PWM Controller subsystem for both positive and negative cycle 46 6.7 Switching Control Subsystem 47 6.8 Switching pattern at switch S4a 47 6.9 Switching pattern at switch S2b 47 6.10 Switching pattern at switch S1a 48 6.11 Switching pattern at switch S3b 48 6.12 Output voltage and output current for fs = 20 kHz 49 6.13 Output voltage and output current for fs = 40 kHz 50 6.14 Output voltage and output current for fs = 80 kHz 50 6.15 Supply current waveform and its THD for fs = 20 kHz 50 6.16 Supply current waveform and its THD for fs = 40 kHz 51 6.17 Supply current waveform and its THD for fs = 80 kHz 51 6.18 Output voltage and output current for fs = 20 kHz 52 6.19 Output voltage and output current for fs = 40 kHz 52 6.20 Output voltage and output current for fs = 80 kHz 53 6.21 Supply current waveform and its THD for fs = 20 kHz 53 6.22 Supply current waveform and its THD for fs = 40 kHz 53 6.23 Supply current waveform and its THD for fs = 80 kHz 54 6.2 6.3 xiv 6.24 Output voltage and output current for fs = 20 kHz 55 6.25 Output voltage and output current for fs = 40 kHz 55 6.26 Output voltage and output current for fs = 80 kHz 55 6.27 Supply current waveform and its THD for fs = 20 kHz 56 6.28 Supply current waveform and its THD for fs = 40 kHz 56 6.29 Supply current waveform and its THD for fs = 80 kHz 57 6.30 Output voltage and output current when driving CPL with fs = 80 kHz 58 6.31 Input voltage and output current when driving CPL with fs = 80 kHz 59 6.32 Supply current waveform and its THD for fs = 80 kHz 59 6.33 Output voltage when driving CPL at different switching frequency 60 6.34 Output current when driving CPL at different switching frequency 60 Supply current when driving CPL with different switching frequency 61 6.36 Supply voltage and current for fs = 20 kHz 62 6.37 Supply voltage and current for fs = 40 kHz 62 6.38 Supply voltage and current for fs = 80 kHz 63 6.35 xv LIST OF ABBREVIATIONS AC - Alternating Current DC - Direct Current AT - Arus Terus AU - Arus Ulang Alik MC - Matrix Converter SPMC - Single Phase Matrix Converter IGBT - Insulated Gate Bipolar transistor PWM - Pulse Width Modulation BJT - Bipolar Junction Transistors SCR - Silicon-Controlled Rectifier MOSFET - Metal-Oxide Semiconductor Field Effect Transistors THD - Total Harmonic Distortion V - Voltage A - Ampere S 1a - Switch 1a S 1b - Switch 1b S 2a - Switch 2a S 2b - Switch 2b S 3a - Switch 3a S 3b - Switch 3b S 4a - Switch 4a S 4b - Switch 4b CHAPTER 1 INTRODUCTION 1.1 Introduction Power electronics circuits convert electric power from one form to another form by using electronic devices. Power electronic circuits function by using semiconductor devices as switches, thereby controlling or modifying a voltage or current. Applications of power electronics range from high power conversion equipment, such as dc transmission and to low power such as power supply for notebook computers [1]. One of the new applications is an advanced circuit topology known as Matrix Converter (MC). The MC circuit topology was first proposed by Gyugyi [2] in 1976 and offers many advantages such as the ability to regenerate energy back to the utility, sinusoidal input and output current and controllable input current displacement factor [3]. Besides, it has the potential of affording an “all silicon” solution for AC-AC conversion, removing the need for reactive energy storage components used in conventional rectifier-inverter based system. Obviously published studies mainly dealt with three-phase circuit topologies [4-6]. The Single-phase matrix converter (SPMC) was first realized by Zuckerberger [7]. Switching strategy for the four quadrant switches is the most important things of matrix converter since it will result in the input source being converted to the desired 2 output through matrix convertion. PWM was used as the switching technique for the four-quadrant switches. Applying the switching strategy and switching technique will produce the desired output that is synthesized from the input source of the matrix converter. There are four types of matrix converter, which relates to the type of power conversion; DC-AC, AC-DC, DC-DC and AC-AC. Since matrix converter was originally introduced, it has received considerable attention because it offers many advantages as described above. The size of the converter is also reduced since there are no large reactive components for energy storage [8]. 1.2 Converter Classification The objective of power electronics circuit is to match the voltage and current requirements of the load to the source. Power electronics circuit convert one type or level of a voltage or current waveform to another, and are hence called converters. Converters are classified by the relationship between input and output [1]. The following are various types of converters that are frequently used to control electric machines. i. AC input to DC output The AC-DC converter produces a DC output from an AC input. Average power is transferred from an AC source to a DC load. The AC-DC converter is specially classified as a rectifier. It is used primarily to control the speed of dc motors. ii. DC input to AC output The DC-AC converter is specially classified as an inverter. An inverter converts a fixed voltage dc to a fixed (or variable) voltage ac 3 with variable frequency. It can be used to control the speed of ac motors. iii. DC input to DC output The DC-DC converter is useful when a load requires a specified (often regulated) DC voltage or current but the source at is at different or unregulated DC value. It is primarily to control the speed of dc motors. iv. AC input to AC output The AC-AC converter may be used to change the voltage level and/or frequency of an AC signal. It can be used to control the speed of an induction motor. 1.3 Objectives The main objective of this project is to design and operate SPMC topology as a controlled rectifier which able to convert AC input signal to DC output signal. Besides, the performances of the SPMC topology when operating as a controlled rectifier driving the constant power load (CPL) will also be studied and analyzed, with the help of a passive damping. 1.4 Scope of Project In order to achieve the objectives that have been stated, there are scopes that will be covered. Apart from converting AC input to DC output signal, the investigation also will be focused on the introduction of Passive Damping network at DC side to improve the total harmonic distortion (THD). The effects on THD over the variation of switching frequency will also be observed. After the entire element has been determined, the performance of SPMC driving a CPL will be examined. 4 The model of CPL was built and detailed performance of its instability characteristic is studied at different CPL power level. The performance on SPMC in term of current THD and output voltage at variable selected frequency and CPL power level also is studied. Lastly the effect on connecting a LC passive filter at the input side was observed. The investigation on the rectifier performances will be carried out using the Matlab Simulink software. 1.5 Thesis Organization The structure of this thesis was carefully planned to give a clear explanation of the overall project. This thesis divided into seven chapters. Chapter 1 briefly explains the introduction of Matrix Converter with other types of converters. The basic theory of converters is also discussed. Chapter 2 describes the overview of a Single Phase Matrix Converter (SPMC). Chapter 3 describes more clearly the switching strategy that involve in the SPMC. In Chapter 4, the instability effect due to source-load interaction and its analysis, as well as passive damping method are explained. Chapter 5 will discusses on the characteristic of the constant power load (CPL). In Chapter 6 brief explanations on a modelling of overall circuit and its simulations are covered. This chapter discussed on the whole system that was produced. In chapter 7, the results obtained from the Modelling and Simulation part being compared to proceed for the conclusion and the recommended for future project was given. 5 CHAPTER 2 SINGLE PHASE MATRIX CONVERTER (SPMC) 2.1 Introduction Basically, SPMC requires 4 bi-directional switches as shown in Figure 2.1 which capable of blocking voltage and conducting current in both directions. The input source of a SPMC circuit can be either a DC or single-phase AC. The output also can be either AC or DC. It’s depends on the switching strategy, and control strategy that will be implement. Figure 2.1: SPMC circuit 6 2.2 Bi-directional Switch Matrix converter composed from a set of bi-directional switch module [8]. This type of switch is one of the circuit characteristics of SPMC. The SPMC requires a bi-directional switch which capable of blocking voltage and conducting current in both directions and switching between states without any delay. However nowadays, there is no discrete semiconductor device that can fulfill the needs. There are two arrangements can be used to create this bi-directional switch either common collector or common emitter. However, the common collector configuration is not practical especially in large system since inductance during commutation can cause problem [9]. Thus the used of common emitter configuration is more practical. The common emitter arrangement consists of two diodes and two IGBTs connected in anti-parallel is shown in Figure 2.2. A pair of diodes provides the reverse blocking capability to the circuit. Each bi-directional switch requires an isolated power supply for the gate drives, but both devices can be driven with respect to the same voltage. Figure 2.2: Bidirectional switch (common emitter arrangement) 7 With bi-directional switch arrangement its will allow each switch independent control of the current in the both direction. Furthermore, this arrangement is reducing the switching losses during the commutation of the load current. This back-to-back bi-directional arrangement of the matrix converter also has lower conduction losses than a diode bridge switch arrangement [10]. 8 CHAPTER 3 SWITCHING STRATEGIES OF SPMC 3.1 Introduction Basically, the particular switching device used in a power electronics circuit depends on the existing state of semiconductor device technology. The behavior of power electronics circuits often is not affected significantly by the actual device used for switching, particularly if voltage drops across a conducting switch are small compared to other circuit voltages. Therefore, semiconductor devices are usually modeled as ideal switches so that circuit behavior can be emphasized. Switches are modeled as short circuits when ON and open circuit when OFF. The power switch devices that always been used in the power converter are IGBT, MOSFET , thyristor and SCR. 3.2 Insulated Gate Bipolar Transistor (IGBT) The selection of power device for a particular application depends not only on the required voltage and current levels but also on its switching characteristic [1]. Insulated gate bipolar transistors or IGBTs, are advanced power control switches similar to high power bipolar transistor, but with an enhanced power saving features designed so that the control power necessary to switch this device is considerably lower than that for a comparable bipolar transistor. 9 The IGBT is an integrated connection of a MOSFET and a BJT which combines all the advantages of both switches. The equivalent circuit for this IGBT is illustrates in Figure 3.1. The drive circuit for the IGBT is like the MOSFET, while the ON-state characteristics are like of the BJT. In simple terms the collector-emitter characteristics are similar to those of the BJT but the control features are those of the MOSFET. The IGBTs are suitable for switching speeds up to 100 kHz and have replaced BJTs in many applications. It consist of three terminals namely collector (C), gate (G), and emitter (E). The symbol shown in Figure 3.2 is more widely used and is the one that we have adopted and mainly used as switches, e.g. in chopper and frequency converter applications. Besides, IGBT is available with ratings of 3300 V and 1200 A. The typical ratings of high-power devices are shown in Table 3.1. Figure 3.1: IGBT Equivalent Circuit 10 Figure 3.2: N-channel IGBT symbol Table 3.1: Typical ratings of high-power devices Availability State of Technology Voltage ratings Current Ratings Switching Frequency On-state voltage Drive circuit THY BJT FET GTO IGBT IGCT Early Late Early Mid 60’s 70’s 80’s 80’s Late 80’s Mid 90’s Mature Mature Rapid Rapid improve improvement 5kV 1kV 500V 5kV 3.3kV 6.5kV 4kA 400A 200A 5kA 1.2kA 4kA Na 5kHz 1MHz 2kHz 100kHz 1kHz 2V 1-2V 2-3V 2-3V 3V Very simple Simple Mature/ improve I*Rds (on) Simple Difficult Very simple Mature Very difficult Cannot Comments turn Phasing Good King in off out in performance very Best overall Replacing using new in high high performance GTO gate product frequency power signals 11 The i-v characteristic of an n-channel IGBT is shown in Figure. 3.3. In the forward direction, qualitatively similar are appearing to those of a logic level bipolar junction transistor except that the controlling parameter is an input voltage, the gatesources voltage, VGS, rather than an input current. The characteristic of a p-channel IGBT would be the same expect that the polarities of the voltages and currents would be reverse. Figure 3.3: IGBT I-V characteristics 3.3 Switching States of SPMC The matrix converter consists of 8 switches, but only 2 switches will operate for each quadrant. The switching strategy which have rectifier action, are concerned with obtaining either a positive and negative group output voltage in such a way to control the output voltage and current. The implementation of AC-to-DC matrix converter requires four bi-directional switches where every two uni-directional switches are connected back to back makes one bi-directional switch. This SPMC which has four switching states is illustrated from Figure 3.4 to 3.7. 12 Figure 3.4: State 1 AC Input (positive cycle) Figure 3.5: State 2 AC Input (negative cycle) 13 Figure 3.6: State 3 AC Input (positive cycle) Figure 3.7: State 4 AC Input (negative cycle) 14 CHAPTER 4 PASSIVE DAMPING NETWORK 4.1 Linear Analysis Technique The root locus technique is a useful tool for analyzing the stability of any system. A system is stable if all of its poles lie on the left-hand side of the s-plane. This technique enables one to use open-loop system transfer function so that the close loop transfer function eigenvalues can be readily obtained. The relative stability and the transient response performance of a closed-loop control system are directly given by location of the closed-loop roots of the characteristic equation. This technique uses the graphical approach which allows the system gain parameter, K, to be changed on the s-plane. The “gain” K could be any system parameter such as a damping resistor that has been used in a passive damping network. Therefore, by simply varying the resistance over a range, the system eigenvalues can be shown on the s-plane. 4.2 Stability Analysis of Impedance Based Criterion Middlebroke has been proposed the analysis of the impedance based stability criterion and it was summarized by Dr. Awang Jusoh as in [11]. To illustrate this concept, a simple system consists of a single source and a single load connected to an interface bus as in Figure 4.1. In this circuit, Vts, Zs, VtL and ZL represent the Thevenin equivalent voltage of the source, impedance of the source, voltage of the 15 load and impedance of the load respectively. The interface bus voltage is given by v, and the currents to the source and load are given by, Is and IL respectively. Figure 4.1: Impedance based stability criterion circuit The voltage at interface, v is given by equation 4.1 [11]. v N L DsVts N s D LVtL ª N D º N L Ds «1 s L » ¬ Ds N L ¼ N L DsVts N s DLVtL ª Z º N L Ds «1 s » ¬ ZL ¼ 4.1 The numerator and denominator of the source denote as Ns and Ds respectively. Similarly for the load is NL and DL. An assumption was made for the load to operate in a stable condition with fed from the ideal voltage source. Besides, for the source it should be able to operate in a stable condition if the load is a constant current source. The denominator part of equation 4.1 shows that if NL and Ds do not have any roots in the right half plane, the system is stable provided that the Nyquist contour of Zs/ZL does not encircle the (-1,0) point. If the magnitude of Zs always less than the magnitude of ZL, there could not be an encirclement of (-1,0) point of the Nyquist plot. This statement is commonly use in design guideline. 16 4.3 L-C Filter Output Impedance, Zo Based on Middlebrook method, the system stability can be examined using the impedance ratio criterion [12]. The simple L-C filter as shown in Figure 4.2 is analysed with Zo is the output impedance of the filter. L Vs C Vc Zo Figure 4.2: Simple L-C filter In order to calculate the output impedance, Zo, the voltage source Vs is assumed to be a short circuited. Therefore, Zo is a combination of the capacitor and inductor in parallel connection. Hence, the output impedance, Zo, becomes as in equation 4.3. 1 Zo Zo 1 jZ L 1 1 jZC jZ L 2 1 jZ LC 4.2 4.3 Another alternative, Laplace Transform method (s-domain) as in Figure 4.3 can be used and resulting equation 4.3 becomes as in equation 4.4. 17 Figure 4.3: L-C Filter in s-domain Zo 1 // sL sC Zo 1 u sL sC 1 sL sC Zo sL s LC 1 4.4 2 The simple L-C filter in Figure 4.2 will have an output impedance characteristic approaching infinity at the resonant frequency of the filter. This will result in the impedance peaking at resonance. The plot of the filter output impedance, Zo, is shown in Figure 4.4. The parameters used are L = 90 μH and C = 500 μH. It shows that at high frequencies, the output impedance of the filter is low because of the low impedance of the capacitor. Then, the output impedance is low at low frequencies because the inductor impedance is low. At resonance, the impedance peaking is severe around 150 dB with this plot resolution. Notice that this is likely to exceed the load converter input impedance, | ZL |, shown dotted in Figure 4.4, and this may cause the system to be unstable. Therefore suitable methods need to be develop so that the severe peaking of the filter output impedance will be prevented. 18 Figure 4.4: Filter output impedance The resonant frequency of the filter is obtained by setting the denominator of equation 4.3 to zero and getting 0 = 4714 rads-1 which is almost similar to the plot in Figure 4.4. Zo 1 LC 1 6 90 x10 x500 x10 6 4714 rads 1 If an effective source resistance, Rs, which consist of the combination of source resistance in series with the resistance of the filter inductor, is taken into account as shown in Figure 4.5, then the output impedance of the second order filter is improved, and is given in equation 4.5. 19 Rs Vs L C Vc Zo Figure 4.5: L-C filter with series resistor Rs Zo sL RS s LC sRS C 1 2 4.5 Figure 4.6 shows the frequency response plot of the output impedance with several values of Rs. Notice that at the frequency resonance, the impedance peaking is very much reduced compared to the plot of Figure 4.4. The impedance peaking of this circuits depends on the values of Rs, where bigger Rs results in lower impedance peaking. Figure 4.6: Output impedance of L-C filter with four different Rs 20 For the small signal stability criterion of the system, the system is guaranteed to be stable if the maximum output impedance, | Zo | max of input filter is less than the magnitude of the input impedance, | ZL |, of the load converter for all frequencies. 4.4 Output to Input Voltage Transfer Function A similar effect can be investigated in the voltage transfer function of the filter [12]. Referring to Figure 4.5, the output to input voltage transfer function is given by equation 4.6 below. A plot of this transfer function is shown in Figure 4.7 for four different values of Rs which are 0.1 , 0.5 , 1 and 1.5 . Vc Vs 1 s LC sRS C 1 4.6 2 Figure 4.7: Voltage transfer function , Vc Vs 21 The plot shows that below the LC resonant frequency, the input voltage passes through the filter without significant attenuation. At the LC resonant frequency, normally peaking in the magnitude plot where the voltage coming out of the filter is higher than the input voltage. The amount of peaking is determined by the resistive losses in the circuit [12]. Notice that peaking is higher as smaller the value of series resistor. 4.5 L-C Filter with Passive Damping Methods By introduction of a series resistance in order to reduce and eliminate the resonant peaking in the filter output impedance has been successfully developed in the previous section, however, this method would be unacceptable due to the high conduction losses in the resistor. Alternatively passive method by Dr. Awang Jusoh has been carried out as in [12] which describe starting in this section until section 4.7. In general, there is some natural damping in the inductor and capacitor due to parasitic components such as equivalent series resistor (esr) in the inductor, however this equivalent series resistor is not normally enough to reduce the impedance peaking. Therefore, by adding the additional series resistance is undesirable as it reduces the system efficiency. Another approach is by connecting a damping resistor in parallel with the capacitor. However this way is not practical since it also creates excessive shunt loss. Placing a combination of a series damping resistor, R, and a capacitor, C2, in parallel with the filter as shown in Figure 4.8 is more practical way. The value of series blocking capacitor, C2, is normally larger than the filter capacitor, C1, for example four times bigger. The series blocking capacitor, C2, is used to block the DC input voltage and prevent DC current from entering the damping resistor, R, which therefore results in a very small conduction loss in the damping resistor. 22 The resonant frequency of L and C1 in the region of o, the impedance of damping capacitor C2 is designed to be small compared with the size of the damping resistor. Therefore, the resistor will perform the normal damping function at the filter resonant frequency. This method of using passive damping is much more efficient than just adding a damping resistor on its own, but still lead to significant system losses under transient conditions. Furthermore, it has the disadvantages of size, weight and cost. Figure 4.8: L-C filter with passive damping network 4.6 Analysis of L-C Filter with Passive Damping Network From the circuit in Figure 4.8, the analysis can be carried out by obtaining the relationship between the output and input voltage and the output impedance of the system. The output impedance of Figure 4.8 is given by equation 4.7. Zo sL1 sRC 2 s LRC1C 2 s 2 LC1 C 2 sRC 2 1 3 4.7 The gain or the output to input voltage ratio is given by equation 4.8 Vc Vs 1 sRC 2 s LRC1C 2 s 2 LC1 C 2 sRC 2 1 3 4.8 23 The characteristic equation (denominator) of equation 4.8 can be rearranged in terms of the parameters of interest as shown in equation 4.9. This equation is used to investigate the damping of the system poles due to the changes of some system parameters. H s R s 2 LC1 C 2 1 s 3 LC1C 2 sC 2 1 K 4.9 To plot the root locus of a closed system which has an open loop transfer function of H(s) and a variable feedback gain K, equation 4.9 is usually used. Here the damping value of the damping resistor is 1 . The roots of the denominator of K H(s) are the “open-loop” poles that are the poles corresponding to a damping resistor of infinity. As expected with a damping resistor of infinity the system poles are on the imaginary axis at r j 1 LC1 . In the root locus plot as the feedback gain K is increased the system poles move towards the zeros, that is the roots of the numerator. Therefore as the damping resistor valued is reduced from infinity to zero, the complex poles will move to the position r j 1 LC1 C 2 . This is illustrated by the root locus plot in Figure 4.9, which shows the plots for several different capacitor ratios. Referring to equation 4.9, the plot as in Figure 4.9 can be obtained by the following command in the Mfile. numgh=[0.000000315 0 1]; G(s)H(s). dengh=([0.000000000135 0 0.003 0]); G(s)H(s). 'G(s)H(s)' GH=tf(numgh,dengh) figure (1) rlocus(GH) hold on % Define numerator of % Define denominator of % % % % Display label Create G(s)H(s) and display. Display figure(1) Draw root locus 24 Figure 4.9 shows that all the poles starting at r j larger values of 1 LC1 r j 4714 rads 1 . With C2 will result in the pole locus extending further into the left-halfC1 plane. For this simulated result, the filter components values are kept as L = 90 μH and C = 500 μH. Using the rlocfind command in MATLAB the damping resistor can be easily found to place the poles at any position on the locus, for example the plot shows that with C2 = 6C1, the poles location of –1.57e+003 ± 1.59e+003 is produced by resistance of 3.7 Figure 4.9: The root locus plot of varying R for different C2. 4.7 Design of the Passive Damping Resistor The characteristic equation of equation 4.8 can be considered in designing the passive damping resistor. This characteristic equation can be approximately factorised as given in equation 4.10. 25 1 sRC 2 L · § s RC 2 1¨ s 2 LC1 s 1¸ R ¹ © Vc Vs 4.10 Equation 4.10 can be rearranged as shown in equation 4.11 1 sRC 2 Vc Vs L· § s 3 LRC1C 2 s 2 LC1 C 2 s¨ RC 2 ¸ 1 R¹ © 4.11 Comparing equation 4.8 and equation 4.11, one realizes that for the approximation to be true, then for the s term of the characteristic equation, R 2 !! L C2 4.12 To have a critical damping of the complex poles that is pole angle on the s plane at zero degrees, then from equation 4.10 2 ªLº «¬ R »¼ 4 LC1 !R 1 L 2 C1 0 0 .5 L C1 4.13 If the parameters of the filter, L and C1 are given, equation 4.13 will be used to calculate the damping resistor, R in order to give critical damping of the poles. The appropriated value for C2 is determined using equation 4.12, for example with L = 90 μH and C = 500 μH, a value of R = 0.212 give the critically damped poles and C2 must be greater than 2mF. Taking 5 times bigger than 2 mF, a value of 10 mF for C2 has been used. 26 To have a design with the complex poles located on the 45° line in the s-plane, then the magnitudes of the real part and the imaginary part of the characteristic equation of equation 4.10 must be equal. ªLº «R» ¬ ¼ 2 2 LC1 !R 1 2 L C1 0.71 L C1 4.14 The value of R will be 0.3 for the filter parameters being considered, and C2 would be chosen to be very much greater than 1 mF. Taking 5 times larger than 1 mF, a value of 5 mF is used. If the damping resistor R is chosen to be L then in the factorised equation, C1 equation 4.10, the pole position angle on the s-plane can be calculated. Substituting for R L will result in the equation : s 2 LC1 s LC1 1 0 . The roots of this C1 equation are given by equation 4.15. s 1r j 3 2 LC1 . 4.15 These roots indicate that the complex poles are located on the 60° line in the s-plane. A damping resistor of R = 0.42 places the poles on the 60° line in the complex plane and the blocking capacitor C2 must be chosen to be very much greater than 0.51 mF. Same as previous, taking 5 times bigger than 0.51mF, a value of 2.5 mF is chosen. 27 As in Figure 4.10, the plot shows the magnitude peaking at the resonant frequency is reduced by the damping circuit. Notice that, value of R = 0.212 and C2 = 10 mH, producing a heavier damping effect. Bode Diagram 20 R=0.42 , C2=2.5 m H R=0.3 , C2=5 m H R=0.212 , C2=10 m H Magnitude (dB) 0 -20 -40 -60 -80 Phase (deg) -100 0 R=0.42 , C2=2.5 m H R=0.3 , C2=5 m H R=0.212 , C2=10 m H -45 -90 -135 -180 2 10 3 10 4 10 5 10 6 10 Frequency (rad/sec) Figure 4.10: Voltage transfer function Vc/Vs of the L-C filter with passive damping where L = 90 μF and C1 = 500 μF 4.8 Design of LC input Filter with Damping Resistor A large transient oscillation in the LC circuit can be damped by using a resistance that is connected to the LC circuit. All electrical engineers understand this concept. The transient can be damped by using a resistor that is connected either in series to or parallel with the inductor or capacitor of the filter. Figure 4.11 shows four possible connection of the resistor (R1, R2, R3, R4) in the LC filter which proposed by Pekik Argo in [13]. 28 Figure 4.11: Possible connection of the resistor Referring to the concept of output to input voltage transfer function, the suitable position of resistor can be determined. Figure 4.12 until 4.15 shows the possible connection of resistor and its transfer function. Vc Vs R s RLC sL R 2 Figure 4.12: Resistor connected in parallel with capacitor and its output to input voltage transfer function Vc Vs sRC 1 s 2 LC sRC 1 Figure 4.13: Resistor connected in series with capacitor and its output to input voltage transfer function 29 Vc Vs sL R s RLC sL 2 Figure 4.14: Resistor connected in parallel with inductor and its output to input voltage transfer function Vc Vs 1 s 2 LC sRC 1 Figure 4.15: Resistor connected in series with inductor and its output to input voltage transfer function Plotting all four transfer functions resulted as in Figure 4.16. The plot shows that the circuit topology of Figure 4.12 (with R1) is less peaking than others. Less peaking means that the system is more stable. Therefore, the position of R1 which is resistor connected in parallel with the capacitor is the most suitable connection to the input LC filter. 30 Figure 4.16: Voltage transfer function for each connection of resistor 31 CHAPTER 5 CONSTANT POWER LOAD 5.1 Introduction With the rapid development and application of distributed power system, Constant Power Load ( CPL ) have turned into a significant type of power consumption devices in aircraft power system. Constant power loads usually present negative impedance characteristic, which is a destabilizing effect to the power system, as in [14]. 5.2 Negative Input Resistance Phenomenon The calculation of the input impedance has been described as in [11]. A block diagram of a constant power load such as an induction motor drive or DC-DC converter are used as shown in Figure 5.1. Since input power, Pin, is a constant, the plot of v-i is in hyperbola form as in Figure 5.2. This illustrates the characteristic of the static input voltage-current for the CPL load. The CPL input resistance, RL, is given by the ratio of small-signal changes in input voltage over the small-signal input current, R L 'v which depends on the 'i converter operating points. The diagram as in Figure 5.2 shows two different slope values of input impedance, RL1 and RL2, at two different points. 32 Notice that, the slope of this characteristic is negative. Therefore the resistance of the converter is known as a negative input resistance where any increment in input voltage will cause a decrease in the input current or vice versa. Figure 5.1: Constant power load Figure 5.2: Static input voltage-current characteristic The elaborate calculation of the negative input resistance is as follows. Since the input power, Pin and output power, Po are equal, Pin Po P And v P i P.i 1 i.v 33 By differentiate the voltage with respect to the current yields, dv di P.i 2 P §P· ¨ ¸ ©v¹ v2 P 2 Since i P v RL 5.1 Equation 5.1 shows the general equation to calculate the small-signal input resistance of a constant power load, CPL. The resistance is in negative value as expected and is also non-linear, depends on the current and voltage. The smaller the RL value, the more negative input will be produced. 5.3 Equilibrium Point The equilibrium points of a system comprising a DC source with non-zero output resistance supplying a constant power load can be examined by using a simple graph method as in Figure 5.3 [12]. The resistance, R presents the source output resistance while the inductor, L and the capacitor, C represent an intermediate filter. Figure 5.3: Model of source connected to CPL via L-C Filter. 34 The DC or steady-state relationships between voltage, v, and current, i, may be written down firstly by considering the constant power load and secondly by considering source. At DC side, inductor, L, is short circuited and capacitor, C, is open circuited. For the load : i.v P 5.2 For the source : v i.R Vs 5.3 The two equations are plotted together in Figure 5.4 for a range of values of resistance, R. The intersection points of the two lines show the possible equilibrium conditions for the circuit. By eliminate i from equation 5.2 and equation 5.3, a quadratic equation is produced for v: v 2 Vs v PR 0 5.4 The solution being: 2 v Vs §V · r ¨ s ¸ RP 2 © 2¹ Equation 5.5 will be used in the testing of simulation CPL model in section 5.4.1. Figure 5.4: Source line and CPL characteristic 5.5 35 5.4 Simulation Model of Constant Power Load, CPL The block diagram consists of a current control source (CCS), a bus voltage measurement, a saturation block, a multiplexer and a function block are built to perform a CPL simulink model as in Figure 5.5. The voltage port, v, and ground, gnd, will be connected to the DC output of SPMC. The CPL power level port, p, is an input signal which defines the load power. Firstly, the voltage measurement block will measure the DC bus voltage, and then pass through to the saturation block. Saturation block is needed to avoid the problem of divide-by-zero error when the voltage measurement approaches values near zero, so that it was set at 0.01 and infinity. After that, the output data will enter the multiplexer together with the second input data which is CPL power. Both data will enter the mathematical block, in which the division of the signal is performed to generate the current signal, which represent the characteristic of the CPL having negative input impedance. Figure 5.5: A block diagram of CPL model 36 5.4.1 L-C Filter with Series Loss Resistor and CPL To begin with, the simulation of schematic diagram as in Figure 5.6 is used to verify the CPL model based on Figure 5.3. A 100 W constant power load supplied from a 270 VDC bus through an L-C filter with series resistor, R, where L = 1 mH, C = 1 μF and R = 20 . Figure 5.7 shows the result of the simulated capacitor voltage and inductor current when the DC source voltage undergoes a transient. Notice that, the DC source voltage abruptly steps from 270 V to 210 V at simulation time 0.01 s and then steps back to 270 V at 0.02 s. The simulation results show lightly-damped oscillations, with the inductor current rising when the source voltage is reduced. The response are more heavily damped with the higher value of source voltage, this is expected since the smallsignal input resistance of CPL has a larger magnitude at higher voltage ( R L Figure 5.6: Simulink block diagram of simulation model. V2 ). P 37 The simulation for a lower input voltage Vs = 200 V was repeated as in Figure 5.8. The DC source voltage abruptly steps from 190 V to 135 V at simulation time 0.01 s and then steps back to 190 V at 0.02 s. The steady state voltage levels in Figure 5.7 and Figure 5.8 may be predicted by the equation 5.5 from the analysis of the circuit as in Figure 5.3. From Figure 5.7 with Vs = 270 V, equation 5.5 predicts the value of Vc to be 262.38 V and with Vs = 200 V as in Figure 5.8, equation 5.5 predicts Vc = 189.44 V. Besides, the multiplication values of capacitor voltage and inductor current is equal to the 100 W. For examples, when Vc = 262.38 V, the iL = 0.38 A which give 99.7 W when multiplied both values. So that, the close values confirms the operation of the CPL simulation model. Figure 5.7: Plot of simulated CPL input voltage, Vc and inductor current, iL at Vs = 270V. 38 Figure 5.8: Plot of simulated CPL input voltage, Vc and inductor current, iL at Vs = 200 V To analyses the small-signal of CPL, the simulation was repeated for much smaller step in Vs of +10V with different CPL power level. Supply voltage is set to Vs = 50 V, and the CPL power level which are set at 10 W, 15 W and 20 W. The results are shown in Figure 5.9 and Figure 5.10. Notice that, as increasing the value of CPL power, the more destabilizing effect occurs. At higher power level such as P = 20 W, the system has more oscillation. It is shows that the system will becomes unstable as increasing the value of CPL power. 39 Figure 5.9: Plot of simulated CPL input voltage, Vc Figure 5.10: Plot of simulated inductor current, iL 40 5.4.2 L-C Filter with Passive Damping and CPL The simulation circuit is shown in Figure 5.11 and the simulation results for 50 V step in Vs are shown in Figure 5.12 for capacitor voltages and for input currents in Figure 5.13. The plot shows a start up transient and then Vs steps from 50 V to 100 V at t = 0.01 s and steps back to 50 V at t = 0.02 s. The component values of input L-C filter and damping network are same as in the previous simulation section 4.6 until 4.7. In this simulation, a CPL is added and the simulation results are shown for three power levels of 1 kW, 2 kW and 3 kW respectively. Figure 5.11: Simulation circuit configuration Both plots show that the system is well damped at each power level. However, when CPL is set at 4 kW, the system will become oscillate as in Figure 5.14. It can be concluded that the system will become unstable up to 3 kW CPL power level. 41 Figure 5.12: Plot of simulated capacitor voltage, Vc for different CPL power values Figure 5.13: Plot of simulated inductor current, iL for different CPL power values Figure 5.14: Plot of simulated capacitor voltage, Vc and inductor current, iL at 4 kW power value. 42 CHAPTER 6 SIMULATION AND DISCUSSION 6.1 Introduction Computer simulation is a valuable analysis and design tool which is emphasized throughout this thesis. Simulation can take on various levels of device and component modeling, depending on the objective of the simulation. Most of the simulation examples and exercises use idealized or default component models. Designing and developing power electronic circuits without suitable computer simulation are extremely laborious, error-prone, time-consuming and expensive. In this thesis, the modeled and simulation of the matrix converter as a controlled rectifier was done by using MATLab/Simulink. 6.2 MATLAB/Simulink Simulink, a companion program to MATLAB is an interactive system for simulating non linear dynamic systems. It is a graphical mouse driven program that allows modeling a system by drawing a block diagram on the screen and manipulating it dynamically. It can work with linear, non linear, continuous-time, discrete time, multivariable and multimate system. The Power System Blockset was designed to provide modern design tools which rapidly and easily build models that simulate power systems. The library contains models of typical power equipment such as transformers, lines machines, and power electronic. For modeling using the 43 Power System Block Set (PSB) within the MATLAB/Simulink (MLS) environment has been simulates by using Simulink toolbox. The Power System Blockset was designed to provide a modern design tool that will allow scientists and engineers to rapidly and easily build models that simulate power systems. Power System Blockset can be rapidly put to work. 6.3 Modelling Design Figure 6.1 shows the overall circuit to implement the LC filter and Passive Damping Network for the rectifier operation driving resistive R load. Besides, Figure 6.2 shows the resistive R load is changed to CPL. There are four measurements to be observed such as voltage and current at supply and load side. Figure 6.3 shows the circuit with adding LC input filter and damping resistor at AC side of the SPMC circuit. The subsystem contain in the SPMC block is shown as in Figure 6.4. SPMC Subsystem itself consists of another four bi-directional switch block which contains a bi-directional switch as in Figure 6.5. To generate the PWM switching sequence as in Figure 6.6, relational block are used to compare both ‘Repeating Sequence’ and ‘Constant’ block. Repeating Sequence represents the switching frequency used, where as the constant block represent the level of amplitude PWM. Then, to get the PWM sequence for both positive and negative side, ‘Compare To Zero’ block and ‘Sine Wave’ block are used and connected to the ‘AND’ block together with the output from the ‘Relational Operator’ where to get the positive PWM, ‘Compare To Zero’ is set to >= 0 while to get the negative PWM is set to <= 0. Figure 6.7 illustrates the switching control subsystem where output from comparing the ‘Compare To Zero’ and ‘Sine wave’ block are connected to ‘OR’ block together with PWM sequence. Next four Figures from Figure 6.8 to Figure 6.11 illustrate the switching pattern for State 1 and State 2 that has been used. 44 Figure 6.1: Overall SPMC circuit connected with LC filter and Passive Damping Network driving a resistive load Figure 6.2: Overall SPMC circuit connected with LC filter and Passive Damping Network driving a CPL 45 Figure 6.3: Overall SPMC circuit connected with LC filter and Passive Damping Network driving a CPL adding with LC input filter and damping resistor Figure 6.4: SPMC Subsystem 46 Figure 6.5: Bidirectional switch Figure 6.6: PWM Controller subsystem for both positive and negative cycle 47 Figure 6.7: Switching Control Subsystem Figure 6.8: Switching pattern at switch S4a Figure 6.9: Switching pattern at switch S2b 48 Figure 6.10: Switching pattern at switch S1a Figure 6.11: Switching pattern at switch S3b 49 6.4 SIMULATION RESULTS 6.4.1 Resistive Load without Filter (L-C1) and Passive Damping Network (R1,C2) For the implementation, by referring to the Figure 6.1, three values of switching frequency, fs are selected which are 20 kHz, 40 kHz and 80 kHz. The parameters used are L = 90 μH, C1 = 500 μF, C2 = 10 mF, R1 = 0.212 and the load resistance, RL = 10 . Figure 6.12 – 6.17 represents the investigation on the system for R load only. Figure 6.12-6.14 represents the output voltage waveform for switching frequency of 20 kHz, 40 kHz and 80 kHz. Next Figure 6.15-6.17 shows the supply current waveform and their THD respectively. Notice that, by increasing the value of switching frequency, fs, THD supply current become smaller. For example, compared to switching frequency for 20 kHz and 80 kHz, the THD supply current for 80 kHz give the smaller values which is 0.6%. However, since the project attention is to get the purely output DC voltage, the LC filter was introduced to solve this problem. Figure 6.12 : Output voltage and output current for fs = 20 kHz 50 Figure 6.13 : Output voltage and output current for fs = 40 kHz Figure 6.14: Output voltage and output current for fs = 80 kHz Figure 6.15: Supply current waveform and its THD for fs = 20 kHz 51 Figure 6.16: Supply current waveform and its THD for fs = 40 kHz Figure 6.17: Supply current waveform and its THD for fs = 80 kHz 52 6.4.2 Adding L-C1 Filter With the insertion of L-C1 filter, the ripple output voltage become smaller as in Figure 6.18-6.20 which shown the waveform of output voltage and output current. By increases the value of switching frequency, the ripple output voltage become smaller. Despite the ripple output voltage was decreased, the THD supply current was increased as shown in Figure 6.21 until Figure 6.23. However, these increments are still under the standard limit which is below 5%. For example, for the switching frequency, fs = 80 kHz, the THD supply current equal to 4.76%. Table 6.1 illustrates the comparisons of THD supply current and ripple output voltage when increase their value of switching frequency. Figure 6.18: Output voltage and output current for fs = 20 kHz Figure 6.19: Output voltage and output current for fs = 40 kHz 53 Figure 6.20: Output voltage and output current for fs = 80 kHz Figure 6.21: Supply current waveform and its THD for fs = 20 kHz Figure 6.22: Supply current waveform and its THD for fs = 40 kHz 54 Figure 6.23: Supply current waveform and its THD for fs = 80 kHz Table 6.1: Comparisons of THD supply current and ripple output voltage with L-C1 Filter Fs( k Hz) THD supply current (%) Ripple output voltage (%) 20 9.49 27 40 5.49 16 80 4.76 8.5 6.4.3 L-C1 Filter with Passive Damping Network (R1,C2) By introduction of Passive Damping Network (R1,C2) as in Figure 6.1, the output ripple voltage becomes smaller. Figures 6.24 - 6.26 show the waveform of output voltage and output current for switching frequency of 20 kHz, 40 kHz and 80 kHz. The ripple output voltage was decreased as increasing the value of switching frequency, fs. Nevertheless, THD supply current was slightly increased as in Figure 6.27 - 6.29. 55 Table 6.2 shows the comparisons of THD supply current and ripple output voltage when increase their value of switching frequency. Figure 6.24: Output voltage and output current for fs = 20 kHz Figure 6.25: Output voltage and output current for fs = 40 kHz Figure 6.26: Output voltage and output current for fs = 80 kHz 56 Figure 6.27: Supply current waveform and its THD for fs = 20 kHz Figure 6.28: Supply current waveform and its THD for fs = 40 kHz 57 Figure 6.29: Supply current waveform and its THD for fs = 80 kHz Table 6.2: Comparisons of THD supply current and ripple output voltage with L-C1 Filter and Passive Damping Network (R1,C2) Fs( k Hz) THD supply current (%) Ripple output voltage (%) 20 9.86 4.5 40 5.87 2.8 80 4.87 2 58 6.4.4 L-C1 filter and Passive Damping Network( R1,C2) driving a CPL Based on Figure 6.2, Figure 6.30 shows the simulated output voltage and output current when the resistive R load was changed to constant power load, CPL using the same parameters L = 90 μH, C1 = 500 μF, C2 = 10 mF and R1 = 0.212 . The CPL power level was set at 100 W with switching frequency, fs = 80 kHz. Notice that, the output current waveform is reflected by the output voltage waveform. So that, the multiplication of both output values is equal to injected power level. However, at the AC side of the SPMC, the supply current becomes discontinuous as in Figure 6.31. The input current THD is shown as in Figure 6.32 which is equal to 45.86%. Figure 6.30: Output voltage and output current when driving CPL with fs = 80 kHz 59 Figure 6.31: Input voltage and output current when driving CPL with fs = 80 kHz Figure 6.32: Supply current waveform and its THD for fs = 80 kHz 60 Figures 6.33 and 6.34 show the simulated output voltage and output current at different switching frequency. The switching frequency was set at 20 kHz, 40 kHz and 80 kHz. The plot shows that as increasing the value of switching frequency, the output voltage will decrease while the output current will increase. Figure 6.33: Output voltage when driving CPL at different switching frequency Figure 6.34: Output current when driving CPL at different switching frequency 61 Figure 6.35 shows the waveform of supply current with different switching frequency. As increasing the value of switching frequency, fs the supply current will become more continuous and less peaking and its TDH are shown in Table 6.3. To overcome this problem, LC input filter with damping resistor was connected at the AC side of the system. Figure 6.35: Supply current when driving CPL with different switching frequency Table 6.3: Comparison of THD supply current when driving CPL at different switching frequency Fs( k Hz) THD supply current (%) 20 98.87 40 74.76 80 45.86 62 6.4.5 Adding LC input filter with Damping Resistor at AC side of the SPMC With the introduction of LC input filter with damping resistor at AC side of the SPMC as in Figure 6.3, the supply current becomes continuous. Figure 6.36-6.38 represents the supply current waveform for each switching frequency of 20 kHz, 40 kHz and 80 kHz. The parameters used are L = 90 μH, C1 = 500 μF, C2 = 10 mF, R1 = 0.212 , Lin = 5 mH, Cin = 45 μF, Rin = 10 and P = 100 W. All simulated waveform supply current are quite similar with each others. Table 5.5 illustrates the THD supply current when increase their value of switching frequency for each Figure 6.36-6.38. Figure 6.36: Supply voltage and current for fs = 20 kHz Figure 6.37: Supply voltage and current for fs = 40 kHz 63 Figure 6.38: Supply voltage and current for fs = 80 kHz Table 6.4: Comparison of THD supply current when driving CPL at different switching frequency after adding LC input filter with damping resistor at AC side Fs( k Hz) 6.5 THD supply current (%) 20 1.95 40 1.65 80 1.24 Discussion From the simulation results SPMC driving R load (no CPL) obtained using Matlab Simulink, it shows that as the value of switching frequency, fs is increased, not only pure DC output voltage obtained but also the THD supply current become more decreased. Besides, the output voltage ripple also decreases by the introduction of LC filter with Passive Damping Network. Table 6.5 shows the tabulated results on the effect of increasing the value of switching frequency, fs. 64 Table 6.5: Effect of increasing value of switching frequency, with R load only (no CPL) Apply LC Filter LC Filter with PDN Ripple THD supply output current (%) voltage (%) 9.86 4.5 Fs (kHz) THD supply current (%) Ripple output voltage (%) 20 9.49 27 40 5.49 16 5.87 2.8 80 4.76 8.5 4.87 2 Referring to the above table, switching frequency at 80 kHz gives the best result between the others. By inserting the Passive Damping Network, output voltage becomes like a purely DC voltage with 1.6% of output ripple voltage. Even though the THD supply current was increased, it still below 5% as required. Table 6.6: Comparison of THD supply current with increasing the switching frequency,with CPL load THD supply current (%) Before apply LC input After apply LC input filter with damping filter with damping resistor resistor 20 98.87 1.95 40 74.76 1.65 80 45.86 1.24 Switching frequency, fs (kHz) Table 6.6 shows the comparison of THD supply current when driving the CPL before and after apply the LC input filter with damping resistor at AC side of the SPMC. It shows that by increasing the value of switching frequency, fs the THD supply current become smaller. There also a big different value of THD after applied the LC input filter with damping resistor. For example at switching frequency, fs = 20 kHz, the different values of THD is 96.92%. 65 CHAPTER 7 CONCLUSION AND FUTURE DEVELOPMENT 7.1 Conclusion The analysis, theoretical design and simulation of a SPMC topology consists of LC Filter with Passive Damping Network was investigated in this project. In the work presented, the stability of the poles on the s-plane has been used to examine the influence of parameters used in designing the LC Filter and Passive Damping Network. This combination of both filters allows the better performance on the SPMC topology with resistive load, RL. It was proven method as a reliable strategy to reduce the THD supply current up to required standard and produce purely output DC voltage. Beside, the SPMC topology which operating as a controlled rectifier with the help of input Filter and damping network also proven to drive the non-linear load such as a constant power load, CPL. 7.2 Future Development Even though input LC passive filter always been considered as good alternative for mitigation, there are still disadvantages exist from this application. This mitigation method cannot be applied in high power application because of the excessive losses in the damping resistor. The damping resistor also will reduce the efficiency of the system. 66 To solve this problem, a virtual resistor that generates no losses can replace the resistor to damp the transient without sacrificing the efficiency as in [12]. On top of that, active damping method can be examined as well to increase the efficiency of the designed system. 67 REFERENCES [1] Daniel W.Hart. “ Introduction To Power Electronic”, Prentice Hall.1997 [2] Gyugyi,L and Pelly,B.R, “Static Power Chargers, Theory, Performance and Application,” John Wiley & Son Inc. 1976 [3] Venturini M., “A New Sine Wave in Sine Wave Out, Conversion Technique Which Eliminates Reactive Elements,” Proceedings Powercon 7,.E3_1-E3_15, 1980. [4] Oyama, J., Higuchi, T., Yamada, E., Koga, T., and Lipo, T., “New Control Strategies for Matrix Converter,” IEEE Power Electron. Spec. Conf. Rec., 1989, pp. 360-367. [5] Sobczyk, T., “Numerical Study of Control Strategies for Frequency Conversion with a Matrix Converter,” Proceedings of Conference on Power Electronics and Motion Control, Warsaw, Poland, 1994, pp. 497-502. [6] Cho, J.G., and Cho, G.H, “Soft-switched Matrix Converter for High Frequency direct AC-to-AC Power Conversion,” Int. J. Electron., 1992, 72, (4), 669-680. [7] Zuckerberger, A., Weinstock, D., Alexandrovitz A., “Single-phase Matrix Converter,” IEE Proc. Electric Power App, Vol.144(4), Jul 1997 pp. 235-240 [8] Alesnia, A & Venturini, M.G.B: “ solid-state power conversion: A Fourier Analysis Approach To Generalized Transformer Synthesis’, IEEE Trans. Circuits & systems,Vol.CAS-28(4), April 1981 [9] Dr. Patrick W. Wheeler, “The Matrix Converter”, Power Electronic, Machine and Control Group. Institute of Electrical Engineer. IEEE, Savoy Place, London [10] M. D. Singh and K. B. Khanchandani, “Power Electronis”, Publisher: Tata McGraw-Hill Publishing Company Limited. 68 [11] Awang bin Jusoh, “The Instability Effect of Constant Power Loads”, IEEE Power Engineering Conference PeCon’04, Nov 2004, Shah Alam, Selangor: IEEE, 175 – 179 [12] Dr. Awang Bin Jusoh, “Active Damping of DC Power Networks”, PhD Thesis. University of Birmingham; Nov 2003. [13] Pekik Argo Dahono, “ A method to Damp Oscillations on the Input LC filter Current-Type AC-DC PWM Converters by Using a Virtual Resistor” IEICE/IEEE INTELEC’03, October 2003, IEEE, 757-761 [14] Yanjun Dong, Wentao Liu, Zhaohui Gao and Xiaobin Zhang, “ Study of a Simulation Model of AC Constant Power Load”, TENCON 2008. IEEE Region 10 Conference , 19-21 Nov 2008, Hyderabad : IEEE, 1 - 5