* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download Adaptive switching frequency buck DC–DC converter with high

Audio power wikipedia , lookup

Ground (electricity) wikipedia , lookup

Power factor wikipedia , lookup

Stepper motor wikipedia , lookup

Electrification wikipedia , lookup

Electric power system wikipedia , lookup

Mercury-arc valve wikipedia , lookup

Utility frequency wikipedia , lookup

Electrical ballast wikipedia , lookup

Three-phase electric power wikipedia , lookup

Power inverter wikipedia , lookup

History of electric power transmission wikipedia , lookup

Voltage regulator wikipedia , lookup

Power engineering wikipedia , lookup

Stray voltage wikipedia , lookup

Voltage optimisation wikipedia , lookup

Surge protector wikipedia , lookup

Electrical substation wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Current source wikipedia , lookup

Amtrak's 25 Hz traction power system wikipedia , lookup

Variable-frequency drive wikipedia , lookup

Mains electricity wikipedia , lookup

Pulse-width modulation wikipedia , lookup

Power MOSFET wikipedia , lookup

Current mirror wikipedia , lookup

Alternating current wikipedia , lookup

Switched-mode power supply wikipedia , lookup

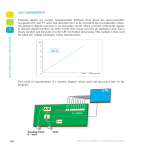

Vol. 36, No. 5 Journal of Semiconductors May 2015 Adaptive switching frequency buck DC–DC converter with high-accuracy on-chip current sensor Jiang Jinguang(江金光) , Huang Fei(黄飞), and Xiong Zhihui(熊智慧) Global Navigation Satellite System Research Center, Wuhan University, Wuhan 430079, China Abstract: A current-mode PWM buck DC–DC converter is proposed. With the high-accuracy on-chip current sensor, the switching frequency can be selected automatically according to load requirements. This method improves efficiency and obtains an excellent transient response. The high accuracy of the current sensor is achieved by a simple switch technique without an amplifier. This has the direct benefit of reducing power dissipation and die size. Additionally, a novel soft-start circuit is presented to avoid the inrush current at the starting up state. Finally, this DC–DC converter is fabricated with the 0.5 m standard CMOS process. The chip occupies 3.38 mm2 . The accuracy of the proposed current sensor can achieve 99.5% @ 200 mA. Experimental results show that the peak efficiency is 91.8%. The input voltage ranges from 5 to 18 V, while a 2 A load current can be obtained. Key words: DC–DC; switching frequency; current sensor; soft-start; wide load range DOI: 10.1088/1674-4926/36/5/055005 EEACC: 2570 1. Introduction The DC–DC converter is in great demand in the field of electric power conversionŒ1 because of its characteristics such as high efficiency, high electric power, extending battery life and providing various supply voltages. In order to design high efficiency DC–DC integrated circuits, numerous methods are introduced. Firstly, a well-known strategy of the sleeping mode by shutting down the unused partial circuitŒ2 is used to reduce the power consumption; it can only enhance efficiency in standby mode but no power can be saved in active mode. Besides, the synchronous rectifier technology is used to achieve a fast transient responseŒ3 , but it has high conduction loss and gate drive loss at light load. Another way, by disabling the negative inductor current at light loadŒ4 , can also improve the efficiency; regrettably, it takes more occupied volumeŒ5 . Since PFM (pulse frequency modulation), which regulates the converter under light load, while PWM (pulse width modulation) regulates the converter under heavy load, can effectively reduce the power consumption, a hybrid mode converter that integrates both PWM and PFM controllersŒ6 is presented in a single chip. However, the efficiency declines when the load is at a medium range. To solve this problem, a multi-mode converter including three modesŒ7 is introduced, whereas it increases the complexity of the circuit configuration. All converters mentioned above utilize one mode or multi-mode to improve efficiency, however, they greatly increase the complexity of the circuit design and consume more chip area. The transition response performance is also affected. A high-accuracy current sensor is essential to design advanced DC–DC converters. It can not only protect the system from large current but also regulate the control loop bet- ter. Diverse current sensors on-chip and off-chip are developed in previous work. The most common way is using an external resistor in series with the inductor or power transistorsŒ8 ; unfortunately, it enlarges the size and suffers from low efficiency. To make an improvement, the method of applying the on-resistance of the power MOSFET instead of the sensing resistors is illustratedŒ9 ; however, the turn-on resistance easily varies with the process, and that will reduce the precision. Another typical means is the integrator techniqueŒ10 by utilizing the inductor voltage to measure the current, but when topologies differ, the design becomes complicated. In order to achieve high accuracy, an amplifierŒ11 is added. Nevertheless, the current sensor suffers from supply voltage limitation. Fortunately, the problem is solved by a low-voltage circuitŒ12 , but the accuracy is limited by the finite gain and bandwidth of the amplifier. Lately, the amplifier is replaced by fewer transistorsŒ13 , whereas the current sources need extra recovering time from OFF station to ON station. This recovering time issue is settled by adding several switchesŒ14 , nevertheless, it still has a sensing current even though the power MOSFET turns off. Finally, the problem of outputting a sensing current when power MOSFET turns off is eliminated with further improvementŒ7 . However, when the power MOSFET turns on, the system may enter into an unbalanced station. In this paper, a current-mode PWM buck DC–DC converter is proposed. This converter focuses on saving die size and achieving high efficiency without sacrificing transient response performance. The converter abandons the multi-mode structure and uses two switching frequencies. The switching frequency can be automatically selected when the load current varies. The converter operates at high frequency under a heavy load while at low frequency under a light load, thus the power balance can be ensured. For that, a lower switching frequency * Project supported by the National Natural Science Foundation of China (No. 41274047), the Natural Science Foundation of Jiangsu Province (No. BK2012639), the Science and Technology Enterprises in Jiangsu Province Technology Innovation Fund (No. BC2012121), and the Changzhou Science and Technology Support (Industrial) Project (No. CE20120074). † Corresponding author. Email: jgjiang09@aliyun.com Received 21 October 2014, revised manuscript received 5 December 2014 © 2015 Chinese Institute of Electronics 055005-1 J. Semicond. 2015, 36(5) Jiang Jinguang et al. Figure 1. Block diagram of the proposed PWM DC–DC buck converter. in PWM mode reduces switching lossesŒ15 , the efficiency is enhanced effectively. This method greatly simplifies the circuit implementation and reduces the occupied volume. What is more, the load transient response is improved efficiently. The proposed current sensor has no amplifier, and it only utilizes a simple switch technique to achieve high accuracy without increasing the quiescent current. This has the direct benefit of reducing power dissipation and die size. The current sensor solves both the problem of outputting sensing current when the power MOSFET turns off and the problem of an unbalanced station, referred to above. In order to suppress the inrush current at the starting up state, a novel soft-start circuit is designed for the converter. Moreover, the soft-start time can be controlled by the capacitor with various sizes. In addition, this converter utilizes two NMOS switches as the power transistors to save the die area and to improve the efficiency. 2. System configuration As shown in Figure 1, the proposed DC–DC buck converter is composed of a power stage and a control network. All functional modules including MOSFET power switches are integrated on a single chip. The two off-chip resistors RF1 and RF2 scale down Vout to VFB . The error amplifier (EA) compares VREF1 with VFB , and amplifies the difference of these two voltages. Then an error signal Vea is obtained and fed to Comparator 1, which is compared with Vcc . VPWM regulates the PWM control module to generate a variable signal of the duty ratio. This variable signal drives the driver logic control module to control the ontime and off-time duration of the power transistors. When the load condition changes, the current sensor detects the inductor current and converts it into Vsense . Then Comparator 2 compares Vsense with VREF2 to build SWTH. SWTH controls the frequency selection module, and an appropriate clock pulse CLK is chosen as the switching frequency. The converter has other necessary modules, among which, the soft-start module is used for start-up protection to suppress the inrush current. In order to protect the circuit from damage, some safety operations such as over current protection (OCP) and over voltage protection (OVP) are performed. Another essential module is the oscillator. It provides different clocks for the entire system. In addition, the Bandgap & Bias module provides the reference voltages and reference currents for the whole system. 3. Circuit implementation 3.1. High accuracy on-chip current sensor To ensure that the converter’s automatic frequency selection operates well, the current variation on the power MOSFET 055005-2 J. Semicond. 2015, 36(5) Jiang Jinguang et al. Figure 2. The proposed current sensor. has to react entirely on the current loop with this highly accurate current sensor. Figure 2 is the schematic of the proposed current sensor, and Figure 3 is the two different operating states of the current sensor. As shown in Figure 2, Q and Q’ come from the driver logic control. The current sensor is realized by matching transistor MS and the power transistor MN1 in the power stage. The aspect ratio of MS is much smaller than that of MN1. MS is implemented by four identical series MOSFETs in the dashed box, so the sensed current does not need an additional circuit to be further scaled down from the load current. Thus the chip area can be reduced to the utmost. Both MC2 and MC3 are biased by Iref generated from the Bandgap; they act as current sources and build identical currents I1 and I2 . As shown in Figure 3(a), when the circuit is under the ONstate, Q is high while Q’ is low. MN1, MS, MQ1 and MQ3 are turned on. MN2, MV and MQ2 are turned off. The node voltage Va is connected to the source of MN1, so Va is equal to VX . VGS of MC4 is maintained constant as I2 is constant. So VC follows the variation of Va . Because I1 and I2 are identical, VGS of MC5 is the same as the VGS of MC4. That means Vb is equal to Va . Then the voltages in the source of MS and MN1 are identical. If the relationship of the aspect ratio between MS and MN1 is 1 : K (K in this paper is 1500), there are the following equationsŒ16 : 1 W IL D n cox K 2 L MS i h (1) 2 VgsMN1 jVTN j VsdMN1 Vsd2M ; N1 Is D 1 n cox 2 W L h MS 2 VgsMS jVTN j VsdMS Vsd2M S i : MN1 and MS will always meet: VsdMN1 D VsdMS ; (3) VgsMN1 D VgsMS : (4) Considering the mismatches of MS and MN1, they are mainly from the threshold voltage mismatches. If the threshold voltage of MS has a tiny variation of VTN , Equation (2) can be expressed as: 1 W Is D n cox 2 L MS h i 2 VgsMS jVTN j VTN VsdMS Vsd2M : (5) S The following equation can be obtained. 2 1 6 Is 61 C D IL K4 VgsMN1 VTN jVTN j 1 Vsd 2 MN1 3 7 7 5: (6) Meanwhile VTN VgsMN1 jVTN j 1 Vsd : 2 MN1 (7) So Is 1 D : (8) IL K As can be seen from Equation (8), IS /IL is constant and independent of VTN , so the influence from the mismatches of MS and MN1 can be ignored. In that I1 D I2 IL ; Is : (9) (2) According to the function of the proposed current sensor, 055005-3 There are following conclusions: Isense D Is D IL ; K (10) J. Semicond. 2015, 36(5) Jiang Jinguang et al. Figure 3. (a) ON-state of current sensor. (b) Off-state of current sensor. Vsense D Isense Rsense : Table 1. Switching frequency under different loads. Load Vsense SWTH CLK Heavy Large 0 OSC1 Light Small 1 OSC2 (11) As can be seen from Equation (10), Isense is reduced with K times of IL , which guarantees high accuracy. The sum current of I1 and I2 is just 6 A, therefore, the efficiency will not be reduced by this current sensor. The proposed current sensor has better performance compared to the current sensor in Reference [6], since it has two problems. The first is that the current sensor in Reference [6] has two current branches, and each branch has two current sources. When the power MOSFET turns on, the two current sources up and down in one branch will be affected by the voltage of the power MOSFET, and it will result in the system entering into a unbalanced station, which is fatal to the system. The second problem is that the current sensed by the current sensor in Reference [6] is still too large for the mode controller, so it has to be scaled down. It indicates that an additional VTI (voltage to current) circuit should be added. The VTI circuit occupies chip area and increases energy consumption, while the proposed current sensor only uses two current sources to establish the circuit, and it has no instability issues. The sensing current is small enough, so it doesn’t need additional circuit to scale down. So the proposed current sensor saves chip area and reduces consumption, which is important for improving efficiency and enhancing circuit stability. In Figure 3(b), when the circuit is under the OFF-state, the voltage of Q is low while Q’ is high. MN1, MS, MQ1 and MQ3 are turned off. MN2, MV and MQ2 are turned on. MV provides a current path for MC2 and MC3. Va and Vb will be pulled up to approach Vin . Since MQ3 is turned off, Isense will be zero. In the next ON station, Va and Vb will follow Vx quickly because I1 and I2 has not been cut-off, thus it will take no time to recover to the normal current. The current sensor in Reference [13] still has a sensing current even though the power MOSFET turns off, because the sensing MOSFET is not totally turned off. Fortunately, the proposed current sensor solves this problem. It adds a switch to cut off the road of the sensing MOSFET, Mrs, so the sensing current is zero when the power MOSFET turns off. The recovering time problem is also avoided, so the performance is improved. The proposed current sensor solves the unbalanced problemŒ6 and has no outputting sensing current when the power MOSFET turns offŒ13 , it achieves better performance. Due to the simple implementation technology without any cascade MOSFET or amplifier, the current sensor has high accuracy, low power consumption and small die area, therefore it can be widely used in very low voltage applications. 3.2. Switching frequency controller In order to realize a DC–DC converter with a simple implementation method and high efficiency, two switching frequencies are used to control the system under different load conditions. The block diagram of the switching frequency controller is presented in Figure 4. PD is an external signal while OSC1, OSC2 and Vsense are internal. The converter’s switching frequency is decided by VREF2 generated by the Bandgap. The switching frequency selection circuit operates when PD is at low voltage level. The current sensor detects the current of the inductor to generate a sensed voltage (Vsense /. When the convert is under the heavy load condition, the sensed current will become larger. That will make Vsense become larger than VREF , and a low voltage level will occur at the output of COM. The fact results that OSC1 is chosen as the switching frequency. For the same reason, when the convert is under the light load condition, the switching frequency will be OSC2. When IL > 150 mA, the load current is heavy and Vsense is large. When IL < 150 mA, the load current is light and Vsense is small. The relationship between the converter’s switching frequency and load condition is shown in Table 1. The sensed current is sampled by the current sensor cycle by cycle, the system’s switching frequency can be chosen dy- 055005-4 J. Semicond. 2015, 36(5) Jiang Jinguang et al. Figure 5. The proposed soft-start circuit. Figure 4. The controller of switching frequency selection. Figure 6. Schematic of the oscillator. namically when the load is updated in every switch cycle. The converter can obtain more rapid response and higher efficiency than that of multi-mode converters. Moreover, the whole system has a simpler and more stable structure. level and EA is shut down. VinC is rising by charging CSS until it is up to Vin , then VEN outputs a low voltage level. The result is that EA starts to operate, that means the soft-start process has been done. The soft-start time (tss / can be calculated as 3.3. Soft-start circuit A novel soft-start circuit is utilized to generate a steadily rising voltage in this paper. The soft-start circuit is different from the conventional one by controlling the enable of the error amplifier. Moreover, the soft start time can be controlled by the capacitor with various sizes. As illustrated in Figure 5, it consists of a current source and a comparator. Vbias2 and Vin come from the bandgap. At the beginning, VinC is zero, VEN is at the high voltage tss D Css Vin : Icharge (12) The charging time can be chosen autonomously according to different sizes of CSS . 3.4. Oscillator The oscillator is used to generate the clocks for the switching frequencies. Figure 6 is the schematic of the oscillator, it 055005-5 J. Semicond. 2015, 36(5) Jiang Jinguang et al. Figure 7. The proposed slope compensation circuit. can generate three main clocks. Part I includes two current sources and a hysteretic comparator to build a clock signal CLKout. Part II includes a frequency divider for generating OSC1, OSC2 and OSCslope. 3.5. Slope compensation circuit When the PWM duty cycle is above 50%, the fixed frequency current-mode buck converters require a linear ramp to avoid sub-harmonic oscillationŒ17 . An artificial ramp can be added as a slope compensation to suppress the sub-harmonic oscillation. The slope compensation circuit of the proposed converter is shown in Figure 7. 4. Simulation and measurement results The proposed DC–DC converter is fabricated in 0.5 m standard CMOS process. The chip microphotograph and the experimental board of the proposed DC–DC converter are shown in Figure 8. The chip size is 1.735 1.950 mm2 and the two power MOSFETs occupy 1.507 1.179 mm2 . This DC– DC converter is simulated with Cadence Spectre and measured by a digital oscilloscope Agilent DS07104A. Figure 8. (a) Chip microphotograph. (b) Experimental board. 4.1. Simulation results Figure 9 shows the simulation results of the current sensor in Figure 2, K is 1500. When Q is at the high voltage level, an accurate sensing current Isense is obtained, but no output current can be observed while Q is low. The maximum accuracy can achieve 99.5% when the load is nearly 200 mA. The simulation results are well consistent with the theoretical estimation. Figure 10 shows the simulation results of the switching frequency controller in Figure 4. When IL < 150 mA, the switching frequency operates at 125 kHz. When IL > 150 mA, the switching frequency operates at 500 kHz. Figure 11 shows the simulation result of the oscillator in Figure 5. CLKout is 1 MHz, OSC1 is 500 kHz, and OSC2 is 125 kHz. Figure 12 shows the different conversion times about the soft-start circuit with various capacitors. Vin D 1 V, Icharge 6 A, when VinC D 1 V, VEN turns to the low voltage level. 055005-6 Figure 9. Simulation results of the current sensor. J. Semicond. 2015, 36(5) Jiang Jinguang et al. Figure 10. Frequency selection under different load conditions. Figure 11. The waveform of different oscillation frequencies. Figure 12. Soft-start time with various capacitors. Table 2 gives the simulation results of the soft-start time and the capacitor’s value; the results are in accordance with Equation (12). Figure 13 gives the simulation results of the system’s dynamic performance when IL steps from 100 to 1500 mA. Vin D 12 V, and the output voltage is about 3.7 V. When the converter operates at light load station, the switching frequency is Figure 13. (a) 1500 to 100 mA load step. (b) 100 to 1500 mA load step. 055005-7 J. Semicond. 2015, 36(5) Capacitor value (nF) Starting time (ms) 1 0.16 Jiang Jinguang et al. Table 2. Soft-start time. 3.25 5.5 0.51 0.86 7.75 10 1.21 1.56 Figure 16. Measured load transient of 1400 mA step. Figure 14. Measured input voltage range. Figure 17. Measured efficiency. frequency and achieve outstanding transient response performance. Figure 17 is the converter’s measured efficiency. When the load range varies from 0.1 to 2000 mA, the overall efficiency is over 75% and the peak efficiency is 91.8%. Table 3 lists the performance of this converter and the comparison with some relevant designsŒ18 20 . Figure 15. Measured soft-start waveform. low and IL is small; when the converter operates at heavy load station, the switching frequency is high and IL is large. The results fully comply with the designed requirements. 4.2. Measurement results Figure 14 shows the test results of the converter’s input voltage range. When Vin is about 5 V, the convert can obtain 3.7 V output voltage. Vout remains a stable voltage of 3.7 V while Vin varies from 5 to 18 V. When Vin is higher than 18 V, the converter’s over voltage protection (OVP) operates. The results indicate that the converter has a wide input voltage range from 5 to 18 V. The soft-start test results are shown in Figure 15. It is easy to achieve a soft-start time of 1.9 ms when the capacitor is 10 nF. Figure 16 gives the converter’s transition results. The output voltage is 3.7 V and the input voltage is 12 V. When IL steps from 100 to 1500 mA, the converter’s switching frequency changes from low to high. The output voltage variation is as low as 2 mV, the maximum output voltage ripple is 14 mV, the load response is 53 mV at 1400 mA step. The results show that the converter can automatically select its switching 5. Conclusions A current-mode PWM buck DC–DC converter is presented in this paper. The proposed converter can automatically select the switching frequency according to the load current condition. In addition, a highly accurate on-chip current sensor is adopted to solve the problem of outputting sensing current when the power MOSFET turns off and the recovering time problem without unbalanced issues. The novel soft-start circuit can achieve a soft-start time of 1.9 ms easily. The maximum load current of this converter is 2 A with a wide input voltage range from 5 to 18 V. Its maximum output voltage ripple is 14 mV and the load response is 53 mV at 1400 mA step. Experimental results show that the peak efficiency is 91.8%. References [1] Shibata K, Pham C. A compact adaptive slope compensation circuit for current-mode DC–DC converter. IEEE International Symposium on Circuits and Systems (ISCAS), 2010: 1651 [2] Benini L, Bogliolo A, de Micheli G. A survey of design techniques for system-level dynamic power management. IEEE 055005-8 J. Semicond. 2015, 36(5) Jiang Jinguang et al. Table 3. Performance list and comparison with other designs. Parameter This work Reference [18] Reference [19] Year 2014 2008 2011 Process (m) 0.5 0.35 0.35 Die size (mm2 / 3.38 3.57 4.70 Input voltage (V) 5–18 2.7–5 2.3–4.8 Output voltage (V) 1–15 >1 0.6–1.8 Load capability (mA) 2000 460 1500 Switching frequency (MHz) 0.125–0.5 0.1–0.6 10 Load transient (mV @ mA) 53 @ 1400 — 8 @ 200 Load regulation (mV/A) 1.5 — 10 Output ripple (mV) 14 36 20 Efficiency (%) 75–91.8 71–95 81–88.4 Trans Very Large Scale Integration (VLSI) Syst, 2000, 8(3): 299 [3] Zhou X, Donati M, Amoroso L. Improved light-load efficiency for synchronous rectifier voltage regulator module. IEEE Trans Power Electron, 2000, 15(5): 826 [4] Zhou X, Wang T G, Lee F C. Optimizing design for low voltage DC–DC converters. Applied Power Electronics Conference and Exposition, 1997, 2: 612 [5] Chen Y T, Chen C H. A DC–DC buck converter chip with integrated PWM/PFM hybrid-mode control circuit. International Conference on Power Electronics and Drive Systems, 2009: 181 [6] Ma F F, Chen W Z, Wu J C. A monolithic current-mode buck converter with advanced control and protection circuits. IEEE Trans Power Electron, 2007, 22(5): 1836 [7] Zhang Chunhong, Yang Haigang, Richard Shi. A wide load range, multi-mode synchronous buck DC–DC converter with a dynamic mode controller and adaptive slope compensation. Journal of Semiconductors, 2013, 34(6): 065003 [8] Forghani-zadeh H P, Rincón-Mora G A. Current-sensing techniques for DC–DC converters. IEEE Midwest Symposium on Circuits and Systems, 2002, 2: 577 [9] Smith T A, Dimitrijev S, Harrison H B. Controlling a DC–DC converter by using the power MOSFET as a voltage controlled resistor. IEEE Trans Circuits Syst I, 2000, 47(3): 357 [10] Midya P, Greuel M, Krein P. Sensorless current mode controlan observer-based technique for DC–DC converters. IEEE Trans Power Electron, 2001, 16(4): 522 [11] Lee C F, Mok P K T. A monolithic current-mode CMOS DC-DC converter with on-chip current-sensing technique. IEEE J SolidState Circuits, 2004, 39(1): 3 Reference [20] 2014 0.5 2.25 2.7–5.5 0.6–4.9 600 4 — 10 16 72–92 [12] Leung C Y, Mok P K T, Leung K N. An integrated CMOS current-sensing circuit for low-voltage current-mode buck regulator. IEEE Trans Circuits Syst II, 2005, 52(7): 394 [13] Chang C H, Chang R C. A novel current sensing circuit for a current-mode control CMOS DC–DC buck converter. IEEE International Symposium on VLSI Design, Automation and Test, 2005: 120 [14] Cheng K H, Su C W, Ko H H. A high-accuracy and high efficiency on-chip current sensing for current-mode control CMOS DC–DC buck converter. IEEE International Conference on Electronics, Circuits and Systems, 2008: 458 [15] Liu Lianxi, Yang Yintang, Zhu Zhangming. A PWM/pseudoPFM auto-mode-applied buck DC–DC switching regulator. Journal of Semiconductors, 2008, 29(10): 1956 [16] Razavi B. Design of analog CMOS integrated circuits. Xi’an: Xi’an Jiaotong University Press, 2003 [17] Li Yanming, Lai Xinquan, Ye Qiang. A current-mode buck DC– DC controller with adaptive on-time control. Journal of Semiconductors, 2009, 30(2): 025007 [18] Liou W R, Yeh M L, Kuo Y L. A high efficiency dual-mode buck converter IC for portable applications. IEEE Trans Power Electron, 2008, 23(2): 667 [19] Yu Jiale, Lü Danzhu, Hong Zhiliang. A 1500 mA, 10 MHz ontime controlled buck converter with ripple compensation and efficiency optimization. Journal of Semiconductors, 2012, 33(1): 015002 [20] Wang H, Hu X, Liu Q. An on-chip high-speed current sensor applied in the current-mode DC–DC converter. IEEE Trans Power Electron, 2014, 29(9): 4479 055005-9