EQUAD Up/Down Clock to Quadrature Encoder

... The EQUAD converts any clock source into optical encoder quadrature outputs. When up clock / down clock mode is selected (via DIP SW1) up-clocks generate an A leads B quadrature sequence and down clocks generate a B leads A quadrature sequence. Alternatively, DIP SW1 may be set for clock and directi ...

... The EQUAD converts any clock source into optical encoder quadrature outputs. When up clock / down clock mode is selected (via DIP SW1) up-clocks generate an A leads B quadrature sequence and down clocks generate a B leads A quadrature sequence. Alternatively, DIP SW1 may be set for clock and directi ...

Pins were added to the layout of the cell so that an LVS test could be

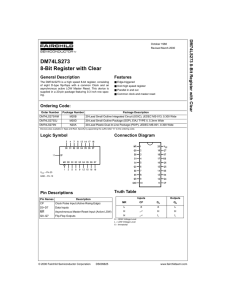

... To simplify the circuit, another version schematic was created. This can be seen in Figure 4. It was verified by another LVS check, whose log can be seen Figure 5. This new schematic clearly shows that the circuit is a D-type flip flop implemented using a master-slave architecture. The constituent l ...

... To simplify the circuit, another version schematic was created. This can be seen in Figure 4. It was verified by another LVS check, whose log can be seen Figure 5. This new schematic clearly shows that the circuit is a D-type flip flop implemented using a master-slave architecture. The constituent l ...

DM7474 Dual Positive-Edge-Triggered D Flip

... positive-edge-triggered D flip-flops with complementary outputs. The information on the D input is accepted by the flip-flops on the positive going edge of the clock pulse. The triggering occurs at a voltage level and is not directly related to the transition time of the rising edge of the clock. Th ...

... positive-edge-triggered D flip-flops with complementary outputs. The information on the D input is accepted by the flip-flops on the positive going edge of the clock pulse. The triggering occurs at a voltage level and is not directly related to the transition time of the rising edge of the clock. Th ...

p6pig - Macmillan Academy

... Explain how the motor will be affected by more light shining on the LDR (3) ...

... Explain how the motor will be affected by more light shining on the LDR (3) ...

current sensor - Electronics DIY

... switched on, there will be a current drain in the primary of the transformer to the negative rail due to an increase in the e.m.f. caused by the flow of current through the appliance. This results in voltage rise at the non-inverting input and the output of IC1 becomes high. This high output drives ...

... switched on, there will be a current drain in the primary of the transformer to the negative rail due to an increase in the e.m.f. caused by the flow of current through the appliance. This results in voltage rise at the non-inverting input and the output of IC1 becomes high. This high output drives ...

ESMT/EMP

... The AD22653 is a 2-Vrms cap-less stereo line driver. The device is ideal for single supply electronics. Cap-less design can eliminate output dc-blocking capacitors for better low frequency response and save cost. The AD22653 is capable of delivering 2-Vrms output into a 10kΩ load with 3.3V supply. T ...

... The AD22653 is a 2-Vrms cap-less stereo line driver. The device is ideal for single supply electronics. Cap-less design can eliminate output dc-blocking capacitors for better low frequency response and save cost. The AD22653 is capable of delivering 2-Vrms output into a 10kΩ load with 3.3V supply. T ...

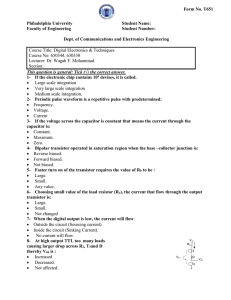

Digital Examination - Philadelphia University Jordan

... None of the above 11- In order to increase the switching speed of MOSFET logic, the channel length must be: Increased. Decreased. Not changed. 12- The number of transistors needed to build a dynamic-NMOS Inverter of n-input is: 2n. n2. n + 2. 13- The advantages of connecting NEMOS & PE ...

... None of the above 11- In order to increase the switching speed of MOSFET logic, the channel length must be: Increased. Decreased. Not changed. 12- The number of transistors needed to build a dynamic-NMOS Inverter of n-input is: 2n. n2. n + 2. 13- The advantages of connecting NEMOS & PE ...

8-bit analog-to-digital converters with differential inputs

... the 256-resistor network. The most significant bit (MSB) is tested first. After eight comparisons (64 clock periods), an 8-bit binary code (1111 1111 = full scale) is transferred to an output latch and the interrupt (INTR) output goes low. The device can be operated in a free-running mode by connect ...

... the 256-resistor network. The most significant bit (MSB) is tested first. After eight comparisons (64 clock periods), an 8-bit binary code (1111 1111 = full scale) is transferred to an output latch and the interrupt (INTR) output goes low. The device can be operated in a free-running mode by connect ...

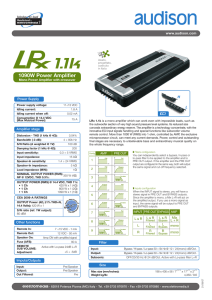

Power Amplifier

... • Emits 120 dB sound power level in the 50—5000 Hz frequency range when used with Norsonic dodecahedron loudspeakers types Nor250 or Nor270 • Wireless remote control of noise generator (optional) • Equalization network to optimise acoustic output from speaker • Balanced signal input for low noise an ...

... • Emits 120 dB sound power level in the 50—5000 Hz frequency range when used with Norsonic dodecahedron loudspeakers types Nor250 or Nor270 • Wireless remote control of noise generator (optional) • Equalization network to optimise acoustic output from speaker • Balanced signal input for low noise an ...

LS7083.PDF

... A high level applied to this input selects X4 mode, a low level selects the X1 mode. Input current is less than 1µA. Do not let this input float. In X4 mode, a clock pulse is generated for every transition of the A or B input. Note that there are 4 transitions per cycle of quadrature code. Thus, a 5 ...

... A high level applied to this input selects X4 mode, a low level selects the X1 mode. Input current is less than 1µA. Do not let this input float. In X4 mode, a clock pulse is generated for every transition of the A or B input. Note that there are 4 transitions per cycle of quadrature code. Thus, a 5 ...

OpAmp Output Protection (posted 16 June, 2016)

... Operational Amplifiers are often used as output drivers and can be subject to output overload, especially when driving loads outside the box. This overload may damage the output driver of the op-amp. An often used circuit includes an output resistor placed between the op amp and the feedback loop as ...

... Operational Amplifiers are often used as output drivers and can be subject to output overload, especially when driving loads outside the box. This overload may damage the output driver of the op-amp. An often used circuit includes an output resistor placed between the op amp and the feedback loop as ...

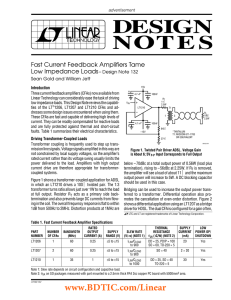

DN132 - Fast Current Feedback Amplifiers Tame Low Impedance Loads

... Driving Transformer-Coupled Loads Transformer coupling is frequently used to step up transmission line signals. Voltage signals amplified in this way are not constrained by local supply voltages, so the amplifier’s rated current rather than its voltage swing usually limits the power delivered to the ...

... Driving Transformer-Coupled Loads Transformer coupling is frequently used to step up transmission line signals. Voltage signals amplified in this way are not constrained by local supply voltages, so the amplifier’s rated current rather than its voltage swing usually limits the power delivered to the ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.