PCM1704

... full-scale performance, high signal-to-noise ratio, and ease of use) with superior low-level performance. This architecture is referred to as sign-magnitude. Two DACs are combined in a complementary arrangement to produce an extremely linear output. The two DACs share a common reference, and a commo ...

... full-scale performance, high signal-to-noise ratio, and ease of use) with superior low-level performance. This architecture is referred to as sign-magnitude. Two DACs are combined in a complementary arrangement to produce an extremely linear output. The two DACs share a common reference, and a commo ...

DAC8043A 数据手册DataSheet 下载

... compatible. The input voltage levels affect the amount of current drawn from the supply; peak supply current occurs as the digital input (VIN) passes through the transition region. See the Supply Current vs. Logic Input Voltage graph located in the typical performance characteristics curves. Maintai ...

... compatible. The input voltage levels affect the amount of current drawn from the supply; peak supply current occurs as the digital input (VIN) passes through the transition region. See the Supply Current vs. Logic Input Voltage graph located in the typical performance characteristics curves. Maintai ...

FEATURES FUNCTIONAL BLOCK DIAGRAM

... The ADG201A-EP is a monolithic CMOS device comprising four independently selectable switches. They are designed on an enhanced LC2MOS process, which gives an increased signal handling capability of ±15 V. These switches also feature high switching speeds and low RON. ...

... The ADG201A-EP is a monolithic CMOS device comprising four independently selectable switches. They are designed on an enhanced LC2MOS process, which gives an increased signal handling capability of ±15 V. These switches also feature high switching speeds and low RON. ...

Question Bank

... b) Design the logic circuit and write a data-flow style VHDL program for the following function. F (P) = ∑A,B,C,D (1,5,6,7,9,13) + d(4,15). 4) Draw and explain in detail of VHDL design flow. 5) a) Write about structural design elements with VHDL code. b) Write a VHDL entity and Architecture for the ...

... b) Design the logic circuit and write a data-flow style VHDL program for the following function. F (P) = ∑A,B,C,D (1,5,6,7,9,13) + d(4,15). 4) Draw and explain in detail of VHDL design flow. 5) a) Write about structural design elements with VHDL code. b) Write a VHDL entity and Architecture for the ...

FEATURES 2.5V ULTRA-PRECISION 1:4 LVDS Precision Edge FANOUT BUFFER/TRANSLATOR

... 14. Total jitter definition: with an ideal clock input frequency of ≤ fMAX (device), no more than one output edge in 1012 output edges will deviate by more than the specified peak-to-peak jitter value. ...

... 14. Total jitter definition: with an ideal clock input frequency of ≤ fMAX (device), no more than one output edge in 1012 output edges will deviate by more than the specified peak-to-peak jitter value. ...

12-Bit R/D Converter with Reference Oscillator AD2S1200

... Sin and Cos mismatch by more than the specified DOS Sin/ Cos mismatch by continuously storing the minimum and maximum magnitude of the monitor signal in internal registers, and calculating the difference between the minimum and maximum. DOS is indicated by a logic low on the DOS pin, and is not latc ...

... Sin and Cos mismatch by more than the specified DOS Sin/ Cos mismatch by continuously storing the minimum and maximum magnitude of the monitor signal in internal registers, and calculating the difference between the minimum and maximum. DOS is indicated by a logic low on the DOS pin, and is not latc ...

TL082 Wide Bandwidth Dual JFET Input Operational Amplifier

... input op amps they do not require special handling. As with most amplifiers, care should be taken with lead dress, component placement and supply decoupling in order to ensure stability. For example, resistors from the output to an input should be placed with the body close to the input to minimize ...

... input op amps they do not require special handling. As with most amplifiers, care should be taken with lead dress, component placement and supply decoupling in order to ensure stability. For example, resistors from the output to an input should be placed with the body close to the input to minimize ...

EVALUATION AND DESIGN SUPPORT

... VGAs and modern ADCs have much greater functionality than the conventional op amps used with early ADC designs. In the VGA used in this example, gain is controlled externally. Pins are provided for selecting between gain values mapped for 10-bit or 12-bit converters, and the impedance of the low noi ...

... VGAs and modern ADCs have much greater functionality than the conventional op amps used with early ADC designs. In the VGA used in this example, gain is controlled externally. Pins are provided for selecting between gain values mapped for 10-bit or 12-bit converters, and the impedance of the low noi ...

AD9901: Ultrahigh Speed Phase/Frequency Discriminator Data Sheet (Rev B, 01/1991)

... Figure 3. Phase-Locked Loop Control System ...

... Figure 3. Phase-Locked Loop Control System ...

MAX6971 16-Port, 36V Constant-Current LED Driver General Description Features

... LE is the latch load input of the MAX6971 that transfers data from the MAX6971 16-bit shift register to its 16-bit latch when LE is high (transparent latch), and latches the data on the falling edge of LE (Figure 2). The fourth input provides output-enable control of the output drivers. OE is high t ...

... LE is the latch load input of the MAX6971 that transfers data from the MAX6971 16-bit shift register to its 16-bit latch when LE is high (transparent latch), and latches the data on the falling edge of LE (Figure 2). The fourth input provides output-enable control of the output drivers. OE is high t ...

DS3695A/DS3695AT/DS3696A Multipoint RS485/RS422 Transceivers

... TRI-STATEÉ bus/line transceivers designed to meet the requirements of EIA standard RS485 with extended common mode range ( a 12V to b7V), for multipoint data transmission. In addition they are compatible with requirements of RS-422. The driver and receiver outputs feature TRI-STATE capability. The d ...

... TRI-STATEÉ bus/line transceivers designed to meet the requirements of EIA standard RS485 with extended common mode range ( a 12V to b7V), for multipoint data transmission. In addition they are compatible with requirements of RS-422. The driver and receiver outputs feature TRI-STATE capability. The d ...

Low Power Designs with CoolRunner-II CPLDs

... Weak Pull-up and Bus Hold All CoolRunner-II CPLDs include I/O termination options to reduce power consumption of the I/O due to externally 3-stated busses. The I/O termination circuitry can be configured in three ways: weak pull-up, bus hold, and no termination. Pull-up and bus hold are selected on ...

... Weak Pull-up and Bus Hold All CoolRunner-II CPLDs include I/O termination options to reduce power consumption of the I/O due to externally 3-stated busses. The I/O termination circuitry can be configured in three ways: weak pull-up, bus hold, and no termination. Pull-up and bus hold are selected on ...

M74HCT04RM13TR - STMicroelectronics

... In order to meet environmental requirements, ST offers these devices in ECOPACK® packages. These packages have a Lead-free second level interconnect. The category of second level interconnect is marked on the package and on the inner box label, in compliance with JEDEC Standard JESD97. The maximum r ...

... In order to meet environmental requirements, ST offers these devices in ECOPACK® packages. These packages have a Lead-free second level interconnect. The category of second level interconnect is marked on the package and on the inner box label, in compliance with JEDEC Standard JESD97. The maximum r ...

Additional Gates and Circuits

... IN is the data input, and EN, the control input. For EN = 0, regardless of the value on IN (denoted by X), the output value is Hi-Z. For EN = 1, the output value follows the input value. ...

... IN is the data input, and EN, the control input. For EN = 0, regardless of the value on IN (denoted by X), the output value is Hi-Z. For EN = 1, the output value follows the input value. ...

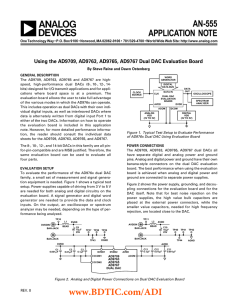

a AN-555 APPLICATION NOTE

... edge of the clock. At this point, SNR should be optimized. Increase the amount of delay for the digital data, moving the transition point closer to the rising edge. As the data transition gets close to the rising edge, SNR will begin to degrade. At this point, on the oscilloscope, measure the time d ...

... edge of the clock. At this point, SNR should be optimized. Increase the amount of delay for the digital data, moving the transition point closer to the rising edge. As the data transition gets close to the rising edge, SNR will begin to degrade. At this point, on the oscilloscope, measure the time d ...

Chap 10

... The jump will be always be associated with a label, which defines the jump to location Several jump instructions can use the same label as the jump location ...

... The jump will be always be associated with a label, which defines the jump to location Several jump instructions can use the same label as the jump location ...

ÿþw w w . d a t a s h e e t 4 u . c o m

... The ALC650 has a 20-bit stereo DAC and 18-bit stereo ADC, full duplex AC'97 2.2 compatible audio CODEC designed for PC multimedia systems, including host/soft audio and AMR/CNR based designs. The ALC650 incorporates proprietary converter technology to achieve a high SNR, greater than 90 dB. The ALC6 ...

... The ALC650 has a 20-bit stereo DAC and 18-bit stereo ADC, full duplex AC'97 2.2 compatible audio CODEC designed for PC multimedia systems, including host/soft audio and AMR/CNR based designs. The ALC650 incorporates proprietary converter technology to achieve a high SNR, greater than 90 dB. The ALC6 ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.