Stepper Motor Driver MC3479

... b) When this pin is opened (raised to VM) such that IBS is <5.0 µA, the internal logic is set to the Phase A condition, and the four driver outputs are put into a high impedance state. The Phase A output (Pin 11) goes active (low), and input signals at the controls are ignored during this time. Upon ...

... b) When this pin is opened (raised to VM) such that IBS is <5.0 µA, the internal logic is set to the Phase A condition, and the four driver outputs are put into a high impedance state. The Phase A output (Pin 11) goes active (low), and input signals at the controls are ignored during this time. Upon ...

Power-Conscious Design of the Cell Processor`s Synergistic

... than the equivalent dynamic approach. To realize a high-frequency design, identifying the speed wall for each macro is critical. At the same time, each circuitry implementation can have different requirements such as area, aspect ratio, porosity, power consumption, noise immunity, and delay. Selecti ...

... than the equivalent dynamic approach. To realize a high-frequency design, identifying the speed wall for each macro is critical. At the same time, each circuitry implementation can have different requirements such as area, aspect ratio, porosity, power consumption, noise immunity, and delay. Selecti ...

RBC-12/17-D48 Series

... CAUTION – This converter is not internally fused. To avoid danger to persons or equipment and to retain safety certification, the user must connect an external fast-blow input fuse as listed in the specifications. Be sure that the PC board pad area and etch size are adequate to provide enough current ...

... CAUTION – This converter is not internally fused. To avoid danger to persons or equipment and to retain safety certification, the user must connect an external fast-blow input fuse as listed in the specifications. Be sure that the PC board pad area and etch size are adequate to provide enough current ...

TD351

... Active Miller clamp The TD351 offers an alternative solution to the problem of Miller current in IGBT switching applications. Instead of driving the IGBT gate to a negative voltage to increase the safety margin, the TD351 uses a dedicated CLAMP pin to control the Miller current. When the IGBT is off ...

... Active Miller clamp The TD351 offers an alternative solution to the problem of Miller current in IGBT switching applications. Instead of driving the IGBT gate to a negative voltage to increase the safety margin, the TD351 uses a dedicated CLAMP pin to control the Miller current. When the IGBT is off ...

Datasheet - Microchip

... 11. Cycle-to-cycle jitter definition: The variation period between adjacent cycles over a random sample of adjacent cycle pairs. TJITTER_CC = Tn – Tn+1, where T is the time between rising edges of the output signal. 12. Total jitter definition: with an ideal clock input frequency of ≤ fMAX (device), ...

... 11. Cycle-to-cycle jitter definition: The variation period between adjacent cycles over a random sample of adjacent cycle pairs. TJITTER_CC = Tn – Tn+1, where T is the time between rising edges of the output signal. 12. Total jitter definition: with an ideal clock input frequency of ≤ fMAX (device), ...

LTC1605-1/LTC1605-2 – Single Supply 16-Bit

... summing junction. This input charge is successively compared with the binary-weighted charges supplied by the capacitive DAC. Bit decisions are made by the high speed comparator. At the end of a conversion, the DAC output balances the VIN input charge. The SAR contents (a 16-bit data word) that repr ...

... summing junction. This input charge is successively compared with the binary-weighted charges supplied by the capacitive DAC. Bit decisions are made by the high speed comparator. At the end of a conversion, the DAC output balances the VIN input charge. The SAR contents (a 16-bit data word) that repr ...

DG508A-09A

... Maxim’s DG508A and DG509A are monolithic CMOS analog multiplexers (muxes): the DG508A is a single 8-channel (1-of-8) mux, and the DG509A is a differential 4-channel (2-of-8) mux. Both devices guarantee break-before-make switching. Maxim guarantees these muxes will not latch up if the power supplies ...

... Maxim’s DG508A and DG509A are monolithic CMOS analog multiplexers (muxes): the DG508A is a single 8-channel (1-of-8) mux, and the DG509A is a differential 4-channel (2-of-8) mux. Both devices guarantee break-before-make switching. Maxim guarantees these muxes will not latch up if the power supplies ...

74AC14 * 74ACT14 Hex Inverter with Schmitt Trigger Input

... 74AC14 • 74ACT14 Hex Inverter with Schmitt Trigger Input General Description The 74AC14 and 74ACT14 contain six inverter gates each with a Schmitt trigger input. They are capable of transforming slowly changing input signals into sharply defined, jitter-free output signals. In addition, they have a ...

... 74AC14 • 74ACT14 Hex Inverter with Schmitt Trigger Input General Description The 74AC14 and 74ACT14 contain six inverter gates each with a Schmitt trigger input. They are capable of transforming slowly changing input signals into sharply defined, jitter-free output signals. In addition, they have a ...

a Dual Sigma-Delta ADC with Auxiliary DAC AD7729

... Digital Power Supply Connection for the Serial Interface Section. This power supply also sets the threshold voltages for RxON, RESETB and MCLK. Digital Ground Connection. ...

... Digital Power Supply Connection for the Serial Interface Section. This power supply also sets the threshold voltages for RxON, RESETB and MCLK. Digital Ground Connection. ...

16-Channel, Current-Input Analog-to

... stops the integration by switching the input signal from side A to side B (SINTA and SINTB). Before the falling edge of CONV, the signal on side B was converted by the ADC and reset during the time that side A was integrating. With the falling edge of CONV, side B starts integrating the input signal ...

... stops the integration by switching the input signal from side A to side B (SINTA and SINTB). Before the falling edge of CONV, the signal on side B was converted by the ADC and reset during the time that side A was integrating. With the falling edge of CONV, side B starts integrating the input signal ...

MAX9115 Single LVDS Line Receiver in SC70 General Description Features

... offset, coupled with the receiver’s 0 to +2.4V input voltage range, allows an approximate ±1V shift in the signal (as seen by the receiver). This allows for a difference in ground references of the driver and the receiver, the common-mode effects of coupled noise, or both. The LVDS standards specify ...

... offset, coupled with the receiver’s 0 to +2.4V input voltage range, allows an approximate ±1V shift in the signal (as seen by the receiver). This allows for a difference in ground references of the driver and the receiver, the common-mode effects of coupled noise, or both. The LVDS standards specify ...

Features

... Current Protection this without impacting the functionality of the circuit, three new features have been added: ...

... Current Protection this without impacting the functionality of the circuit, three new features have been added: ...

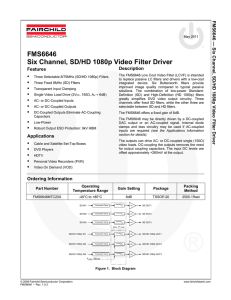

FMS6646 Six Channel, SD/HD 1080p Video Filter Driver Description

... by 150mv therefore VOUT = 2*VIN DC+150mv. This offset is required to obtain optimal performance from the output driver and is held at the minimum value in order to decrease the standing DC current into the load. Since the FMS6646 has a 2x (6dB) gain, the output is typically connected via a 75Ω serie ...

... by 150mv therefore VOUT = 2*VIN DC+150mv. This offset is required to obtain optimal performance from the output driver and is held at the minimum value in order to decrease the standing DC current into the load. Since the FMS6646 has a 2x (6dB) gain, the output is typically connected via a 75Ω serie ...

Dual Channel High-IP3 100MHz – 6GHz Active Mixer ADL5802 Preliminary Technical Data

... input linearity, SSB Noise Figure, and DC current to be optimized using a single control pin. The high input linearity allows the device to be used in demanding cellular applications where in-band blocking signals may otherwise result in degradation in dynamic performance. The balanced active mixer ...

... input linearity, SSB Noise Figure, and DC current to be optimized using a single control pin. The high input linearity allows the device to be used in demanding cellular applications where in-band blocking signals may otherwise result in degradation in dynamic performance. The balanced active mixer ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.