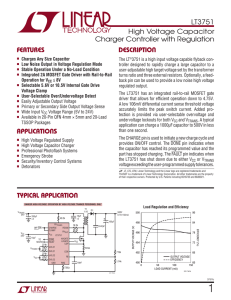

LT3751 - High Voltage Capacitor Charger Controller with Regulation

... Note 5: Refer to Block Diagram for VTRANS and VDRAIN definitions. Note 6: Low noise regulation of the output voltage requires a resistive voltage divider from output voltage to FB pin. FB pin should not be grounded in this configuration. Refer to the Typical Application diagram for proper FB pin con ...

... Note 5: Refer to Block Diagram for VTRANS and VDRAIN definitions. Note 6: Low noise regulation of the output voltage requires a resistive voltage divider from output voltage to FB pin. FB pin should not be grounded in this configuration. Refer to the Typical Application diagram for proper FB pin con ...

1 GS/s, Low Power Flash Technology

... 1.1. Background The signals in the real world are analog for example light, sound, etc. In order to digitally process any analog signal we need to convert the analog signal into digital form by using a circuit called analog-to-digital converter. Whenever we need the analog signal back, digital-to-a ...

... 1.1. Background The signals in the real world are analog for example light, sound, etc. In order to digitally process any analog signal we need to convert the analog signal into digital form by using a circuit called analog-to-digital converter. Whenever we need the analog signal back, digital-to-a ...

SN74LVC1G175-EP 数据资料 dataSheet 下载

... PREVIEW: Device has been announced but is not in production. Samples may or may not be available. OBSOLETE: TI has discontinued the production of the device. ...

... PREVIEW: Device has been announced but is not in production. Samples may or may not be available. OBSOLETE: TI has discontinued the production of the device. ...

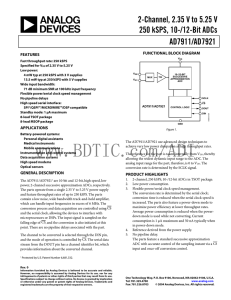

AD7911 数据手册DataSheet下载

... Data In. Logic input. The channel to be converted is provided on this input and is clocked into an internal register on the falling edge of SCLK. Serial Clock. Logic input. SCLK provides the serial clock for accessing data from the part. This clock input is also used as the clock source for the AD79 ...

... Data In. Logic input. The channel to be converted is provided on this input and is clocked into an internal register on the falling edge of SCLK. Serial Clock. Logic input. SCLK provides the serial clock for accessing data from the part. This clock input is also used as the clock source for the AD79 ...

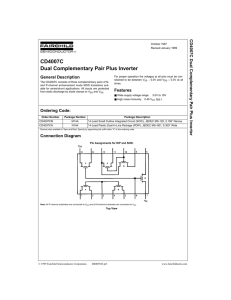

Fairchild ChipFind - Manufacturer datasheet and components

... device or system whose failure to perform can be reawhich, (a) are intended for surgical implant into the sonably expected to cause the failure of the life support body, or (b) support or sustain life, and (c) whose failure device or system, or to affect its safety or effectiveness. to perform when ...

... device or system whose failure to perform can be reawhich, (a) are intended for surgical implant into the sonably expected to cause the failure of the life support body, or (b) support or sustain life, and (c) whose failure device or system, or to affect its safety or effectiveness. to perform when ...

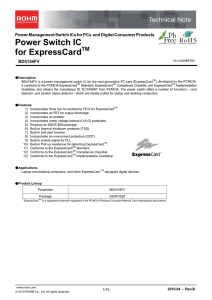

BD4154FV

... (with the standby circuit current of 40 μA), It discharges each output and lowers output voltage when the input falls to 0.8 volts or less. V3_IN, V15_IN, and V3AUX_IN These are the input terminals for each channel of a 3ch switch. V3_IN and V15_IN terminals have two pins each, which should be short ...

... (with the standby circuit current of 40 μA), It discharges each output and lowers output voltage when the input falls to 0.8 volts or less. V3_IN, V15_IN, and V3AUX_IN These are the input terminals for each channel of a 3ch switch. V3_IN and V15_IN terminals have two pins each, which should be short ...

802.3at PSE Load Compliance Testing

... At startup, all PD’s, even “Type 2” PD’s that require up to 25.5 watts, must initially turn on with load levels equal to or less than PD’s that are fully compliant to the 802.3af specification today. PD’s must be given the permission by PSE’s, either through a new physical layer classification signa ...

... At startup, all PD’s, even “Type 2” PD’s that require up to 25.5 watts, must initially turn on with load levels equal to or less than PD’s that are fully compliant to the 802.3af specification today. PD’s must be given the permission by PSE’s, either through a new physical layer classification signa ...

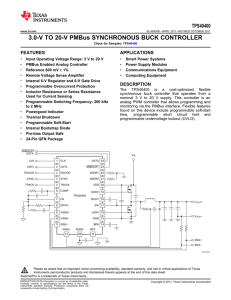

3.0-V TO 20-V PMBus SYNCHRONOUS BUCK CONTROLLER TPS40400 FEATURES APPLICATIONS

... See applications section for more information regarding soft-start time setting. Ensured by design. Not production tested. The entire current ripple waveform must reside inside the linear range for current reading results to be accurate. DC current level must be zero or greater for accurate results. ...

... See applications section for more information regarding soft-start time setting. Ensured by design. Not production tested. The entire current ripple waveform must reside inside the linear range for current reading results to be accurate. DC current level must be zero or greater for accurate results. ...

BDTIC www.BDTIC.com/infineon Efficient Lighting Intelligent solutions for LED drivers and lamp ballast control

... The TLE 4309G is an integrated adjustable constant current source for driving loads up to 500mA. The output current level can be adjusted with an external shunt resistor. Supplying high-power LEDs with the TLE 4309G ensures constant brightness independent from supply voltage or LED forward voltage ...

... The TLE 4309G is an integrated adjustable constant current source for driving loads up to 500mA. The output current level can be adjusted with an external shunt resistor. Supplying high-power LEDs with the TLE 4309G ensures constant brightness independent from supply voltage or LED forward voltage ...

Series-Parallel ac Networks

... undertaken earlier. The circuits to be discussed will have only one source of energy, either potential or current. Networks with two or more sources will be considered in Chapters 17 and 18, using methods previously described for dc circuits. In general, when working with series-parallel ac networks ...

... undertaken earlier. The circuits to be discussed will have only one source of energy, either potential or current. Networks with two or more sources will be considered in Chapters 17 and 18, using methods previously described for dc circuits. In general, when working with series-parallel ac networks ...

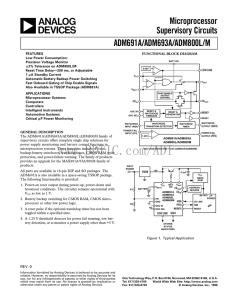

ADM691A 数据手册DataSheet 下载

... Output Voltage, VCC or VBATT is internally switched to VOUT depending on which is at the highest potential. When VCC is higher than VBATT and is also higher than the reset threshold, VCC is switched to VOUT. When VCC is lower than VBATT and below the reset threshold, VBATT is switched to VOUT. Conne ...

... Output Voltage, VCC or VBATT is internally switched to VOUT depending on which is at the highest potential. When VCC is higher than VBATT and is also higher than the reset threshold, VCC is switched to VOUT. When VCC is lower than VBATT and below the reset threshold, VBATT is switched to VOUT. Conne ...

MAX12529 Dual, 96Msps, 12-Bit, IF/Baseband ADC General Description Features

... The MAX12529 is a dual, 96Msps, 12-bit analog-to-digital converter (ADC) featuring fully differential wideband track-and-hold (T/H) inputs, driving internal quantizers. The MAX12529 is optimized for low power, small size, and high dynamic performance in intermediate frequency (IF) and baseband sampl ...

... The MAX12529 is a dual, 96Msps, 12-bit analog-to-digital converter (ADC) featuring fully differential wideband track-and-hold (T/H) inputs, driving internal quantizers. The MAX12529 is optimized for low power, small size, and high dynamic performance in intermediate frequency (IF) and baseband sampl ...

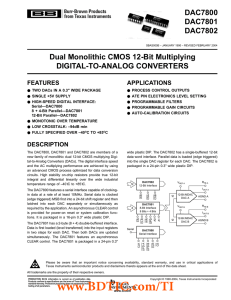

DAC7800 数据资料 dataSheet 下载

... The DAC7800 features a serial interface capable of clockingin data at a rate of at least 10MHz. Serial data is clocked (edge triggered) MSB first into a 24-bit shift register and then latched into each DAC separately or simultaneously as required by the application. An asynchronous CLEAR control is ...

... The DAC7800 features a serial interface capable of clockingin data at a rate of at least 10MHz. Serial data is clocked (edge triggered) MSB first into a 24-bit shift register and then latched into each DAC separately or simultaneously as required by the application. An asynchronous CLEAR control is ...

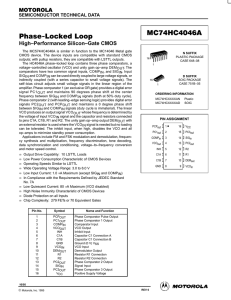

Phase-Locked Loop MC74HC4046A

... four flip–flops and some gating logic, a three state output and a phase pulse output as shown in Figure 6. This comparator acts only on the positive edges of the input signals and is independent of duty cycle. Phase comparator 2 operates in such a way as to force the PLL into lock with 0 phase diffe ...

... four flip–flops and some gating logic, a three state output and a phase pulse output as shown in Figure 6. This comparator acts only on the positive edges of the input signals and is independent of duty cycle. Phase comparator 2 operates in such a way as to force the PLL into lock with 0 phase diffe ...

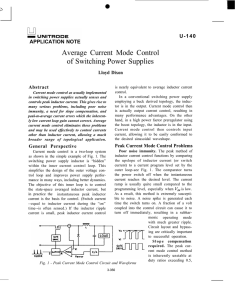

harmonic reduction in a single-switch three-phase

... or diode rectifiers. Since these rectifiers draw non-sinusoidal currents or reactive power from the source, the power quality of the distribution network is greatly deteriorated, resulting in low efficiency of utilities. Recently, more and more stringent limits on the level of harmonics promote the ...

... or diode rectifiers. Since these rectifiers draw non-sinusoidal currents or reactive power from the source, the power quality of the distribution network is greatly deteriorated, resulting in low efficiency of utilities. Recently, more and more stringent limits on the level of harmonics promote the ...

$doc.title

... four flip–flops and some gating logic, a three state output and a phase pulse output as shown in Figure 6. This comparator acts only on the positive edges of the input signals and is independent of duty cycle. Phase comparator 2 operates in such a way as to force the PLL into lock with 0 phase diffe ...

... four flip–flops and some gating logic, a three state output and a phase pulse output as shown in Figure 6. This comparator acts only on the positive edges of the input signals and is independent of duty cycle. Phase comparator 2 operates in such a way as to force the PLL into lock with 0 phase diffe ...

GTL2006PW

... leak to the power supply if they are pulled high while the device is unpowered. The GTL inputs will also not leak to the power supply under the same conditions. The LVTTL totem pole outputs, however, are not open drain type outputs and there will be current flow on these pins if they are pulled high ...

... leak to the power supply if they are pulled high while the device is unpowered. The GTL inputs will also not leak to the power supply under the same conditions. The LVTTL totem pole outputs, however, are not open drain type outputs and there will be current flow on these pins if they are pulled high ...

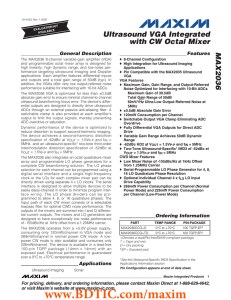

General Description Features

... high linearity, high dynamic range, and low-noise performance targeting ultrasound imaging and Doppler applications. Each amplifier features differential inputs and outputs and a total gain range of 50dB (typ). In addition, the VGAs offer very low output-referred noise performance suitable for inter ...

... high linearity, high dynamic range, and low-noise performance targeting ultrasound imaging and Doppler applications. Each amplifier features differential inputs and outputs and a total gain range of 50dB (typ). In addition, the VGAs offer very low output-referred noise performance suitable for inter ...