power electronics - SK Engineering Academy

... Design of filter is difficult, interference with commutation signals. 13. What is Time ratio control? The Time ratio control (δ) is the ratio between t on to the total time period (T) i.e δ = ton T By varying the ton period the output voltage can be controlled and this sis Called as time ratio contr ...

... Design of filter is difficult, interference with commutation signals. 13. What is Time ratio control? The Time ratio control (δ) is the ratio between t on to the total time period (T) i.e δ = ton T By varying the ton period the output voltage can be controlled and this sis Called as time ratio contr ...

AD7813 数据手册DataSheet下载

... protection for the analog inputs. Care must be taken to ensure that the analog input signal never exceeds the supply rails by more than 200 mV. This will cause these diodes to become forward biased and start conducting current into the substrate. The maximum current these diodes can conduct without ...

... protection for the analog inputs. Care must be taken to ensure that the analog input signal never exceeds the supply rails by more than 200 mV. This will cause these diodes to become forward biased and start conducting current into the substrate. The maximum current these diodes can conduct without ...

Wideband, Fixed Gain, JFET-Input AMPLIFIER OPA653 FEATURES DESCRIPTION

... The OPA653 is a very broadband, voltage-feedback amplifier with internal gain-setting resistors that set a fixed gain of +2 V/V or -1 V/V and a high-impedance JFET-input stage. Its very high bandwidth of 500 MHz can be used to either deliver high signal bandwidths at a gain of +2 V/V or, if driven f ...

... The OPA653 is a very broadband, voltage-feedback amplifier with internal gain-setting resistors that set a fixed gain of +2 V/V or -1 V/V and a high-impedance JFET-input stage. Its very high bandwidth of 500 MHz can be used to either deliver high signal bandwidths at a gain of +2 V/V or, if driven f ...

LF198/LF298/LF398, LF198A/LF398A Monolithic Sample-and-Hold Circuits LF198/LF298/LF398, LF198A/LF398A

... Sample error to moving input signals probably causes more confusion among sample-and-hold users than any other parameter. The primary reason for this is that many users make the assumption that the sample and hold amplifier is truly locked on to the input signal while in the sample mode. In actualit ...

... Sample error to moving input signals probably causes more confusion among sample-and-hold users than any other parameter. The primary reason for this is that many users make the assumption that the sample and hold amplifier is truly locked on to the input signal while in the sample mode. In actualit ...

DS1372 General Description Features

... Real-Time Clocks (RTCs). An external 32.768kHz oscillator can be used as the DS1372’s time base. In this configuration, the X1 pin is connected to the external oscillator signal and the X2 is floated. The EOSC bit in the Control Register controls oscillator operation. ...

... Real-Time Clocks (RTCs). An external 32.768kHz oscillator can be used as the DS1372’s time base. In this configuration, the X1 pin is connected to the external oscillator signal and the X2 is floated. The EOSC bit in the Control Register controls oscillator operation. ...

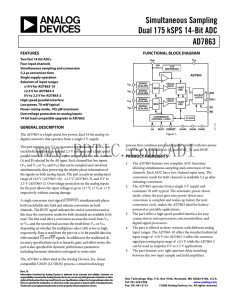

AD7863 数据手册DataSheet下载

... Digital Ground. Ground reference for digital circuitry. Convert Start Input. Logic input. A high-to-low transition on this input puts both track/holds into their hold mode and starts conversion on both channels. Data Bit 6 to Data Bit 0. Three-state TTL outputs. Analog Ground. Ground reference for m ...

... Digital Ground. Ground reference for digital circuitry. Convert Start Input. Logic input. A high-to-low transition on this input puts both track/holds into their hold mode and starts conversion on both channels. Data Bit 6 to Data Bit 0. Three-state TTL outputs. Analog Ground. Ground reference for m ...

Series Resonance

... Series Resonance – VR, VL, and VC Plotting the magnitude (effective value) of the voltage VR, VL, and VC and the current I versus frequency for the series resonant circuit on the same set of axes, we obtain the curves shown in Fig.20.17. Note that the VR curve has the same shape as the I curve and ...

... Series Resonance – VR, VL, and VC Plotting the magnitude (effective value) of the voltage VR, VL, and VC and the current I versus frequency for the series resonant circuit on the same set of axes, we obtain the curves shown in Fig.20.17. Note that the VR curve has the same shape as the I curve and ...

MAX710EVKIT

... varies above and below the regulated output voltage. It can be set in two modes: one optimized for lowest noise, the other for highest efficiency. The MAX710 EV kit is a fully assembled and tested surface-mount circuit board. It can also be used to evaluate the MAX711, which has an adjustable output ...

... varies above and below the regulated output voltage. It can be set in two modes: one optimized for lowest noise, the other for highest efficiency. The MAX710 EV kit is a fully assembled and tested surface-mount circuit board. It can also be used to evaluate the MAX711, which has an adjustable output ...

TPS40090 数据资料 dataSheet 下载

... latter method involves generation of a current proportional signal with an R-C circuit (shown in Figure 10). The R-C values are selected by matching the time constants of the R-C circuit and the inductor; R-C = L/DCR. With either current sense method, the current signal is amplified and superimposed ...

... latter method involves generation of a current proportional signal with an R-C circuit (shown in Figure 10). The R-C values are selected by matching the time constants of the R-C circuit and the inductor; R-C = L/DCR. With either current sense method, the current signal is amplified and superimposed ...

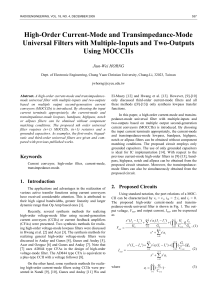

64

... novel design method for an RDC and procedure for the position and speed estimation is required, Phase Locked selecting the components for the desired RDC bandwidth. Loop (PLL) based tracking loops, are used. In [7] a RDC The main features of the proposed RDC method are: high method is illustrated th ...

... novel design method for an RDC and procedure for the position and speed estimation is required, Phase Locked selecting the components for the desired RDC bandwidth. Loop (PLL) based tracking loops, are used. In [7] a RDC The main features of the proposed RDC method are: high method is illustrated th ...

ADA4898-1

... The ADA4898-1 is available in an 8-lead, 150 mil SOIC package that features an exposed metal paddle to improve power dissipation and heat transfer to the negative supply plane. This EPAD offers a significant thermal relief over the traditional plastic packages. The ADA4898-1 is rated to work over th ...

... The ADA4898-1 is available in an 8-lead, 150 mil SOIC package that features an exposed metal paddle to improve power dissipation and heat transfer to the negative supply plane. This EPAD offers a significant thermal relief over the traditional plastic packages. The ADA4898-1 is rated to work over th ...

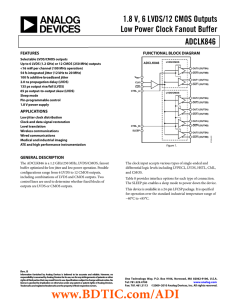

1.8 V, 6 LVDS/12 CMOS Outputs Low Power Clock Fanout Buffer ADCLK846

... The clock input accepts various types of single-ended and differential logic levels including LVPECL, LVDS, HSTL, CML, and CMOS. Table 8 provides interface options for each type of connection. The SLEEP pin enables a sleep mode to power down the device. This device is available in a 24-pin LFCSP pac ...

... The clock input accepts various types of single-ended and differential logic levels including LVPECL, LVDS, HSTL, CML, and CMOS. Table 8 provides interface options for each type of connection. The SLEEP pin enables a sleep mode to power down the device. This device is available in a 24-pin LFCSP pac ...

Processing of Communication Signal Using Operational

... around a flat portion of the input signal the output of the switch will be alternate in polarity (i.e. its magnitude changes between positive and negative values alternatively). As a result, transconductance of OTA3 (gm3) will assume a low value. Consequently, from equation (8) it can be concluded th ...

... around a flat portion of the input signal the output of the switch will be alternate in polarity (i.e. its magnitude changes between positive and negative values alternatively). As a result, transconductance of OTA3 (gm3) will assume a low value. Consequently, from equation (8) it can be concluded th ...

Paper Title (use style: paper title) - Infoscience

... feed-forward path almost does not exist which improves the stability. Another benefit of the cascode compensation is that it results in better power supply rejection ratio (PSRR) [6]. Besides the advantages there are some limitations as well that will be discussed during the presentation of the desi ...

... feed-forward path almost does not exist which improves the stability. Another benefit of the cascode compensation is that it results in better power supply rejection ratio (PSRR) [6]. Besides the advantages there are some limitations as well that will be discussed during the presentation of the desi ...

LF198/LF298/LF398, LF198A/LF398A Monolithic Sample-and-Hold Circuits LF198/LF298/LF398, LF198A/LF398A

... Sample error to moving input signals probably causes more confusion among sample-and-hold users than any other parameter. The primary reason for this is that many users make the assumption that the sample and hold amplifier is truly locked on to the input signal while in the sample mode. In actualit ...

... Sample error to moving input signals probably causes more confusion among sample-and-hold users than any other parameter. The primary reason for this is that many users make the assumption that the sample and hold amplifier is truly locked on to the input signal while in the sample mode. In actualit ...

lecture6

... Slides by ‘Pearson Education’ for Electronic Devices by Floyd ‘Op.amp for every one’ by Ron Mancini ’Stability Analysis for volatge feedback op-amps’, ...

... Slides by ‘Pearson Education’ for Electronic Devices by Floyd ‘Op.amp for every one’ by Ron Mancini ’Stability Analysis for volatge feedback op-amps’, ...

Input Offset Voltage

... Input offset voltage Input bias current Common-mode rejection ratio (CMRR) Slew rate The peak output voltage swing ...

... Input offset voltage Input bias current Common-mode rejection ratio (CMRR) Slew rate The peak output voltage swing ...

An Si–SiGe BiCMOS Direct-Conversion Mixer With Second-Order and Third-Order Nonlinearity

... The use of direct-conversion techniques is a promising approach for highly integrated wireless receivers due to their potential for low-power fully monolithic operation and extremely broad bandwidth [6]. Their potential for broad-band operation is especially important for future wireless communicati ...

... The use of direct-conversion techniques is a promising approach for highly integrated wireless receivers due to their potential for low-power fully monolithic operation and extremely broad bandwidth [6]. Their potential for broad-band operation is especially important for future wireless communicati ...