Configuration Quick Start Guidelines Summary

... When using a JTAG Chain with mixed voltage devices, as shown in Figure 5, extra care must be taken to ensure the integrity between the devices. Refer to the device's data sheet for the appropriate voltage operating ranges. In this example, using a 5V, 3.3V, and 2.5V device in a single JTAG chain, al ...

... When using a JTAG Chain with mixed voltage devices, as shown in Figure 5, extra care must be taken to ensure the integrity between the devices. Refer to the device's data sheet for the appropriate voltage operating ranges. In this example, using a 5V, 3.3V, and 2.5V device in a single JTAG chain, al ...

MSP430-JTAG-ISO-MK2 USER’S MANUAL professional MSP430 programmer/debugger Revision J, April 2014

... recognized device. Depending on the mode of operation you choose (debugger, mass storage or stand alone) a driver might be required for proper operation. If the driver is installed properly and you are in stand-alone mode new device should be recognized properly by the device manager. You need to in ...

... recognized device. Depending on the mode of operation you choose (debugger, mass storage or stand alone) a driver might be required for proper operation. If the driver is installed properly and you are in stand-alone mode new device should be recognized properly by the device manager. You need to in ...

BitBlaster Serial Cable Data Sheet

... Programs/configures a single device or multiple devices in a chain Supports data transfer rates from 9,600 to 230,400 baud ...

... Programs/configures a single device or multiple devices in a chain Supports data transfer rates from 9,600 to 230,400 baud ...

Technical Specification

... The remote control feature allows to be PG4UW software flow controlled by other application – either using .BAT file commands or using DLL file. DLL file, examples (C/PAS/VBASIC/.NET) and manual are part of standard software delivery. Jam files of JEDEC standard JESD-71 are interpreted by Jam Player ...

... The remote control feature allows to be PG4UW software flow controlled by other application – either using .BAT file commands or using DLL file. DLL file, examples (C/PAS/VBASIC/.NET) and manual are part of standard software delivery. Jam files of JEDEC standard JESD-71 are interpreted by Jam Player ...

ICE-1000/ICE-2000 Emulator User`s Guide, Revision 1.1

... 2. Disconnect the USB cable between the emulator and the PC. 3. Power down the target board. 4. The emulator can now be removed from the target. For custom processor boards still in design, refer to an Engineer-to-Engineer Note, “Analog Devices JTAG/SWD Emulation Technical Reference (EE-68)”, availa ...

... 2. Disconnect the USB cable between the emulator and the PC. 3. Power down the target board. 4. The emulator can now be removed from the target. For custom processor boards still in design, refer to an Engineer-to-Engineer Note, “Analog Devices JTAG/SWD Emulation Technical Reference (EE-68)”, availa ...

Alice1 pixel readout chip

... •Translates data into Glink compatible 800Mbit/s stream of data on an optical link, which will provide the connection from the MCM to the control room •It was already developed at CERN •It’s tested and fully functional ...

... •Translates data into Glink compatible 800Mbit/s stream of data on an optical link, which will provide the connection from the MCM to the control room •It was already developed at CERN •It’s tested and fully functional ...

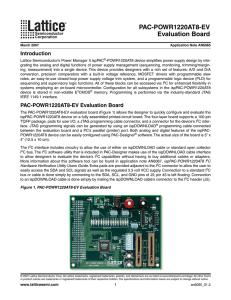

ispPAC-POWR1220AT8 Evaluation Board

... Several red LEDs are also provided on the evaluation board to indicate proper function and as aids to debugging. LED D2 indicates that the on-board 3.3V supply is powered up. LED D3 is connected to the ispPACPOWR1220AT8 device’s TDO line, and will briefly flash when downloading, indicating that down ...

... Several red LEDs are also provided on the evaluation board to indicate proper function and as aids to debugging. LED D2 indicates that the on-board 3.3V supply is powered up. LED D3 is connected to the ispPACPOWR1220AT8 device’s TDO line, and will briefly flash when downloading, indicating that down ...

Bt878/879

... 2. On page 79 of the Bt878/Bt879 datasheet, it erroneously states the following: “In addition to the 24 I/O bits, the GPIO port includes an interrupt pin, and a write enable pin. The GPINTR signal sets the bit in the interrupt register and causes an interrupt condition to occur.” It should state the ...

... 2. On page 79 of the Bt878/Bt879 datasheet, it erroneously states the following: “In addition to the 24 I/O bits, the GPIO port includes an interrupt pin, and a write enable pin. The GPINTR signal sets the bit in the interrupt register and causes an interrupt condition to occur.” It should state the ...

TWR-K20D50M Manual

... ‐500 ns conversion time achievable with programmable delay block triggering ‐Two high‐speed comparators providing fast and accurate motor over‐current protection by driving PWMs to a safe state ‐Optional analog voltage reference provides an accurate reference to analog blocks and replaces exter ...

... ‐500 ns conversion time achievable with programmable delay block triggering ‐Two high‐speed comparators providing fast and accurate motor over‐current protection by driving PWMs to a safe state ‐Optional analog voltage reference provides an accurate reference to analog blocks and replaces exter ...

EE-305: Designing and Debugging Systems with SHARC Processors

... Most of the commonly used SPI flash devices require a falling edge on chip select (/CS) prior to the start of an instruction after power up. For ADSP-2126x and ADSP-21362/3/4/5/6 processors, pull up the SPI flash chip select using a 4.7kΩ resistor. These SHARC processors do not actively provide logi ...

... Most of the commonly used SPI flash devices require a falling edge on chip select (/CS) prior to the start of an instruction after power up. For ADSP-2126x and ADSP-21362/3/4/5/6 processors, pull up the SPI flash chip select using a 4.7kΩ resistor. These SHARC processors do not actively provide logi ...

Advanced Boundary Scan and BSDL

... Says which logical signals comprise the TAP Specify which input port logic values enable JTAG compliance (part can either conform to JTAG or refuse to conform) Instruction register description: Length Op Codes -- can add optional instructions Mapping from bit patterns to instruction Op Codes ...

... Says which logical signals comprise the TAP Specify which input port logic values enable JTAG compliance (part can either conform to JTAG or refuse to conform) Instruction register description: Length Op Codes -- can add optional instructions Mapping from bit patterns to instruction Op Codes ...

APPLICATION NOTE Designing With XC9500XL CPLDs

... required delivery site. In this case, two cascade times are required to provide 18 product terms. Note that the solution is not unique. The software could just as well encounter an adjacent neighbor with locked down product terms and been forced to skip over another macrocell to satisfy its need. Th ...

... required delivery site. In this case, two cascade times are required to provide 18 product terms. Note that the solution is not unique. The software could just as well encounter an adjacent neighbor with locked down product terms and been forced to skip over another macrocell to satisfy its need. Th ...

Xilinx FPGAs:Evolution and Revolution

... 4 DLLs VCCINT – 1.8V More speed grades than Spartan-II. Less packaging Options. ...

... 4 DLLs VCCINT – 1.8V More speed grades than Spartan-II. Less packaging Options. ...

JTAG-SMT2-NC™ Programming Module for Xilinx® FPGAs Overview

... system designer with the ability to choose the type of USB connector and its location on the system board. Features include: ...

... system designer with the ability to choose the type of USB connector and its location on the system board. Features include: ...

TWR-K21D50M Tower Module Freescale Semiconductor, Inc. 1 TWR-K21D50M Contents

... 500-ns conversion time achievable with programmable delay block triggering Two high-speed comparators providing fast and accurate motor over-current protection by driving PWMs to a safe state Optional analog voltage reference provides an accurate reference to analog blocks and replaces external volt ...

... 500-ns conversion time achievable with programmable delay block triggering Two high-speed comparators providing fast and accurate motor over-current protection by driving PWMs to a safe state Optional analog voltage reference provides an accurate reference to analog blocks and replaces external volt ...

doc2562

... These signals are TCK, TDO, TDI, TMS, VTref and GND. Optional line is the nSRST. The nTRST signal is not used, and is reserved for compatibility with other equipment. nSRST is used to control and monitor the target reset line - this is not necessary for correct emulation. However if the application ...

... These signals are TCK, TDO, TDI, TMS, VTref and GND. Optional line is the nSRST. The nTRST signal is not used, and is reserved for compatibility with other equipment. nSRST is used to control and monitor the target reset line - this is not necessary for correct emulation. However if the application ...

Architecting DFT into Board Design to Leverage Board

... Sets the outputs of the device to logic levels determined by the contents of the boundary-scan register and selects the bypass register to be connected between TDI and TDO. Before loading this instruction, the contents of the boundary-scan register can be preset with the SAMPLE/PRELOAD instruction. ...

... Sets the outputs of the device to logic levels determined by the contents of the boundary-scan register and selects the bypass register to be connected between TDI and TDO. Before loading this instruction, the contents of the boundary-scan register can be preset with the SAMPLE/PRELOAD instruction. ...

BMR-AVR-AMCm-pb - Pigeon Point Systems

... The bench top implementation of this reference design is the same H8S-based bench top used with the BMR-H8S-ATCA reference design. This board already implements two AMC sites and an MMC at each site, based the BMR-AVR-AMCm reference design. In addition, the board includes the needed Carrier IPMC fun ...

... The bench top implementation of this reference design is the same H8S-based bench top used with the BMR-H8S-ATCA reference design. This board already implements two AMC sites and an MMC at each site, based the BMR-AVR-AMCm reference design. In addition, the board includes the needed Carrier IPMC fun ...

Minutes of CMS FED Design Meeting Wednesday November 6th 2002

... Comment: Can only reprogram VME FPGA from EPROM. And can only program EPROM via JTAG test chain (i.e. external cable). Need to consider in-situ programming option for VME FPGA in next iternation. VME 3 Comment JTAG chain (buffer arrangement) should work but it may not be optimised for speed. Test se ...

... Comment: Can only reprogram VME FPGA from EPROM. And can only program EPROM via JTAG test chain (i.e. external cable). Need to consider in-situ programming option for VME FPGA in next iternation. VME 3 Comment JTAG chain (buffer arrangement) should work but it may not be optimised for speed. Test se ...

LPC-MT-2138

... RTC code (EW-ARM) RS232 code (EW-ARM) Button, Relay, LED, buzzer demo code (EW-ARM) LCD, RTC, UART, BUTTONs, BUZZER demo code (GNU) by Markus ...

... RTC code (EW-ARM) RS232 code (EW-ARM) Button, Relay, LED, buzzer demo code (EW-ARM) LCD, RTC, UART, BUTTONs, BUZZER demo code (GNU) by Markus ...

In-System Programming Design Guidelines for ispJTAG Devices

... As stated earlier, the ideal scheme for buffering includes buffers at both ends of the cable and buffers for each group of five to eight devices in the programming chain. This case does not cover all situations, however. For example, in a design with only two devices in the chain, the question arise ...

... As stated earlier, the ideal scheme for buffering includes buffers at both ends of the cable and buffers for each group of five to eight devices in the programming chain. This case does not cover all situations, however. For example, in a design with only two devices in the chain, the question arise ...

Hello, and welcome to this presentation of the STM32 general

... SPI and others share the same I/O pins in order to interface with the external environment. Peripherals are configured through an alternate function multiplexer which ensures that only one peripheral is connected to the I/O pin at a single time. Of course, this selection can be changed during run ti ...

... SPI and others share the same I/O pins in order to interface with the external environment. Peripherals are configured through an alternate function multiplexer which ensures that only one peripheral is connected to the I/O pin at a single time. Of course, this selection can be changed during run ti ...

a Engineer-to-Engineer Note EE-281

... simulation may be appropriate. IBIS models that can assist with signal simulation are available from the Analog Devices web site. ...

... simulation may be appropriate. IBIS models that can assist with signal simulation are available from the Analog Devices web site. ...

NanoMind A3200 Datasheet

... used to interface to external I2C components. For interfacing with SPI devices the board has one external connection with three chip selects and it also has 8 inputs to an ADC and if needed the ADC inputs can also be used as GPIO. The form factor of the A3200 fits on the GomSpace NanoDock’s, which m ...

... used to interface to external I2C components. For interfacing with SPI devices the board has one external connection with three chip selects and it also has 8 inputs to an ADC and if needed the ADC inputs can also be used as GPIO. The form factor of the A3200 fits on the GomSpace NanoDock’s, which m ...